Other Parts Discussed in Thread: SN74LVC1G125,

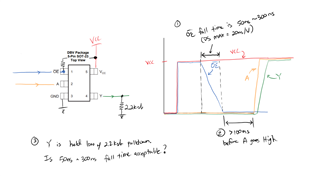

Below I attached an image of a use-case for the SN74AUC1G125 and SN74LVC1G125.

Basically, the datasheet states Δt/Δv is 20ns(max) when VCC = 1.5V, and 10ns(max) when VCC = 1.8V.

1) This goes for the xOE as well, right?

2) If the fall time to bring xOE LOW and activate the device is too long (50ns~300ns), then the output could flip back and forth between Hi-Z and driven, right?

3) For #2 above, what if A was LOW, and Y was pulled LOW via 2.2kΩ resistor, until >100ms after xOE was pulled low?

In this case, even if the output flips back and forth between Hi-Z and driven, it will still be LOW, right?

Is this an "allowable" violation of the Δt/Δv max limitation - since the output can only be LOW during the xOE fall transition?