Dear Champs,

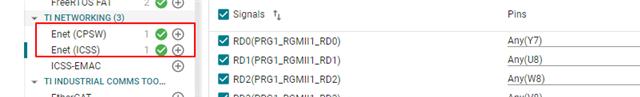

Is it possible to use Enet(CPSW) and Enet(ICSS) together?

When my customer tried to make Enet(CPSW) and Enet(ICSS) to be active in syscfg together as below, they find errors caused by same name conflict in some variables and functions of 'tidrivers_config.c'.

They enabled Enet(CPSW) and Enet(ICSS) together as below.

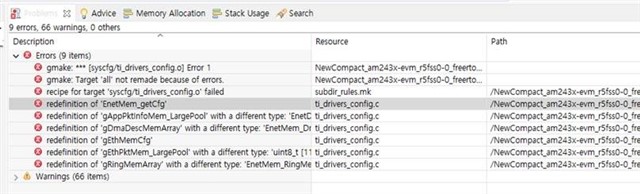

The error was occurred in CCS as below.

The generated ti_drivers_config.c file and syscfg file are in below.

/*

* Copyright (C) 2021 Texas Instruments Incorporated

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the

* distribution.

*

* Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*/

/*

* Auto generated file - DO NOT MODIFY

*/

#include "ti_drivers_config.h"

#include <drivers/sciclient.h>

/*

* I2C

*/

/* I2C atrributes */

static I2C_HwAttrs gI2cHwAttrs[CONFIG_I2C_NUM_INSTANCES] =

{

{

.baseAddr = CSL_I2C0_CFG_BASE,

.intNum = 193,

.eventId = 0,

.funcClk = 96000000U,

.enableIntr = 1,

.ownSlaveAddr =

{

0x1C,

0x1C,

0x1C,

0x1C,

},

},

{

.baseAddr = CSL_I2C1_CFG_BASE,

.intNum = 194,

.eventId = 0,

.funcClk = 96000000U,

.enableIntr = 1,

.ownSlaveAddr =

{

0x1C,

0x1C,

0x1C,

0x1C,

},

},

};

/* I2C objects - initialized by the driver */

static I2C_Object gI2cObjects[CONFIG_I2C_NUM_INSTANCES];

/* I2C driver configuration */

I2C_Config gI2cConfig[CONFIG_I2C_NUM_INSTANCES] =

{

{

.object = &gI2cObjects[CONFIG_I2C0],

.hwAttrs = &gI2cHwAttrs[CONFIG_I2C0]

},

{

.object = &gI2cObjects[CONFIG_I2C1],

.hwAttrs = &gI2cHwAttrs[CONFIG_I2C1]

},

};

uint32_t gI2cConfigNum = CONFIG_I2C_NUM_INSTANCES;

/*

* IPC Notify

*/

#include <drivers/ipc_notify.h>

#include <drivers/ipc_notify/v0/ipc_notify_v0.h>

/* this function is called within IpcNotify_init, this function returns core specific IPC config */

void IpcNotify_getConfig(IpcNotify_InterruptConfig **interruptConfig, uint32_t *interruptConfigNum)

{

/* extern globals that are specific to this core */

extern IpcNotify_InterruptConfig gIpcNotifyInterruptConfig_r5fss0_0[];

extern uint32_t gIpcNotifyInterruptConfigNum_r5fss0_0;

*interruptConfig = &gIpcNotifyInterruptConfig_r5fss0_0[0];

*interruptConfigNum = gIpcNotifyInterruptConfigNum_r5fss0_0;

}

/*

* IPC RP Message

*/

#include <drivers/ipc_rpmsg.h>

/* Number of CPUs that are enabled for IPC RPMessage */

#define IPC_RPMESSAGE_NUM_CORES (5U)

/* Number of VRINGs for the numner of CPUs that are enabled for IPC */

#define IPC_RPMESSAGE_NUM_VRINGS (IPC_RPMESSAGE_NUM_CORES*(IPC_RPMESSAGE_NUM_CORES-1))

/* Number of a buffers in a VRING, i.e depth of VRING queue */

#define IPC_RPMESSAGE_NUM_VRING_BUF (8U)

/* Max size of a buffer in a VRING */

#define IPC_RPMESSAGE_MAX_VRING_BUF_SIZE (256U)

/* Size of each VRING is

* number of buffers x ( size of each buffer + space for data structures of one buffer (32B) )

*/

#define IPC_RPMESSAGE_VRING_SIZE RPMESSAGE_VRING_SIZE(IPC_RPMESSAGE_NUM_VRING_BUF, IPC_RPMESSAGE_MAX_VRING_BUF_SIZE)

/* VRING base address, all VRINGs are put one after other in the below region.

*

* IMPORTANT: Make sure of below,

* - The section defined below should be placed at the exact same location in memory for all the CPUs

* - The memory should be marked as non-cached for all the CPUs

* - The section should be marked as NOLOAD in all the CPUs linker command file

*/

/* In this case gRPMessageVringMem size is 46720 bytes */

uint8_t gRPMessageVringMem[IPC_RPMESSAGE_NUM_VRINGS][IPC_RPMESSAGE_VRING_SIZE] __attribute__((aligned(128), section(".bss.ipc_vring_mem")));

/*

* MMCSD

*/

/* MMCSD attributes */

static MMCSD_Attrs gMmcsdAttrs[CONFIG_MMCSD_NUM_INSTANCES] =

{

{

.ctrlBaseAddr = CSL_MMCSD0_CTL_CFG_BASE,

.ssBaseAddr = CSL_MMCSD0_SS_CFG_BASE,

.inputClkFreq = 200000000U,

.intrNum = 165U,

.intrEnable = FALSE,

.enableDma = TRUE,

.phyType = MMCSD_PHY_TYPE_HW_PHY,

.cardType = MMCSD_CARD_TYPE_EMMC,

.busWidth = MMCSD_BUS_WIDTH_8BIT,

.supportedModes = MMCSD_SUPPORT_MMC_DS | MMCSD_SUPPORT_MMC_HS_SDR,

.tuningType = MMCSD_PHY_TUNING_TYPE_AUTO,

},

{

.ctrlBaseAddr = CSL_MMCSD1_CTL_CFG_BASE,

.ssBaseAddr = CSL_MMCSD1_SS_CFG_BASE,

.inputClkFreq = 200000000U,

.intrNum = 166U,

.intrEnable = FALSE,

.enableDma = TRUE,

.phyType = MMCSD_PHY_TYPE_SW_PHY,

.cardType = MMCSD_CARD_TYPE_SD,

.busWidth = MMCSD_BUS_WIDTH_4BIT,

.supportedModes = MMCSD_SUPPORT_SD_DS | MMCSD_SUPPORT_SD_HS,

.tuningType = MMCSD_PHY_TUNING_TYPE_AUTO,

},

};

/* MMCSD objects - initialized by the driver */

static MMCSD_Object gMmcsdObjects[CONFIG_MMCSD_NUM_INSTANCES];

/* MMCSD driver configuration */

MMCSD_Config gMmcsdConfig[CONFIG_MMCSD_NUM_INSTANCES] =

{

{

&gMmcsdAttrs[CONFIG_MMCSD0],

&gMmcsdObjects[CONFIG_MMCSD0],

},

{

&gMmcsdAttrs[CONFIG_MMCSD1],

&gMmcsdObjects[CONFIG_MMCSD1],

},

};

uint32_t gMmcsdConfigNum = CONFIG_MMCSD_NUM_INSTANCES;

/*

* Enet DMA memory allocation utility functions.

*/

/* ========================================================================== */

/* Include Files */

/* ========================================================================== */

#include <string.h>

#include <enet.h>

#include <include/core/enet_utils.h>

#include <include/core/enet_dma.h>

#include "enet_appmemutils.h"

#include "enet_appmemutils_cfg.h"

#include "enet_apputils.h"

#define PKT_POOL_ENABLE 1U

/* ========================================================================== */

/* Structure Declarations */

/* ========================================================================== */

#if defined (ENET_SOC_HOSTPORT_DMA_TYPE_UDMA)

/* Enet UDMA DESC memories */

static EnetMem_DmaDescMemPoolEntry gDmaDescMemArray[(((0U) * ENET_CFG_TX_CHANNELS_NUM) +

((0U) * ENET_CFG_RX_FLOWS_NUM))]

__attribute__ ((aligned(ENETDMA_CACHELINE_ALIGNMENT),

section(".bss:ENET_DMA_DESC_MEMPOOL")));

/* RX & TX RingAcc memories */

static EnetMem_RingMemPoolEntry gRingMemArray[((0U) *

(ENET_CFG_TX_CHANNELS_NUM + ENET_CFG_RX_FLOWS_NUM))]

__attribute__ ((aligned(ENETDMA_CACHELINE_ALIGNMENT),

section(".bss:ENET_DMA_RING_MEMPOOL")));

#endif

#if (PKT_POOL_ENABLE == 1)

/* Eth packet info memory Q - large pool */

static EnetDma_Pkt gAppPktInfoMem_LargePool[(((0U) * ENET_CFG_RX_FLOWS_NUM) +

((0U) * ENET_CFG_TX_CHANNELS_NUM))];

/* Eth packet large pool memories */

static uint8_t gEthPktMem_LargePool[(((0U) * ENET_CFG_RX_FLOWS_NUM) +

((0U) * ENET_CFG_TX_CHANNELS_NUM))][ENET_MEM_LARGE_POOL_PKT_SIZE]

__attribute__ ((aligned(ENETDMA_CACHELINE_ALIGNMENT),

section(".bss:ENET_DMA_PKT_MEMPOOL")));

#endif

static const EnetMem_Cfg gEthMemCfg =

{

#if (PKT_POOL_ENABLE == 1)

.pktBufPool =

{

[ENET_MEM_POOLIDX_LARGE] =

{

.pktSize = ENET_MEM_LARGE_POOL_PKT_SIZE,

.numPkts = (((0U) * ENET_CFG_RX_FLOWS_NUM) +

((0U) * ENET_CFG_TX_CHANNELS_NUM)),

.pktInfoMem = gAppPktInfoMem_LargePool,

.pktInfoSize = sizeof(gAppPktInfoMem_LargePool),

.pktBufMem = &gEthPktMem_LargePool[0][0],

.pktBufSize = sizeof(gEthPktMem_LargePool),

},

},

#else

.pktBufPool =

{

[ENET_MEM_POOLIDX_LARGE] =

{

.pktSize = 0,

.numPkts = 0,

.pktInfoMem = NULL,

.pktInfoSize = 0,

.pktBufMem = NULL,

.pktBufSize = 0,

},

},

#endif

#if defined (ENET_SOC_HOSTPORT_DMA_TYPE_UDMA)

.ringMem =

{

.numRings = ((0U) *

(ENET_CFG_TX_CHANNELS_NUM + ENET_CFG_RX_FLOWS_NUM)),

.ringMemBase = gRingMemArray,

.ringMemSize = sizeof(gRingMemArray),

},

.dmaDescMem =

{

.numDesc = (((0U) * ENET_CFG_TX_CHANNELS_NUM) +

((0U) * ENET_CFG_RX_FLOWS_NUM)),

.descMemBase = gDmaDescMemArray,

.descMemSize = sizeof(gDmaDescMemArray),

},

#endif

};

const EnetMem_Cfg * EnetMem_getCfg(void)

{

return &gEthMemCfg;

}

/*

* Enet DMA memory allocation utility functions.

*/

/* ========================================================================== */

/* Include Files */

/* ========================================================================== */

#include <string.h>

#include <enet.h>

#include <include/core/enet_utils.h>

#include <include/core/enet_dma.h>

#include "enet_appmemutils.h"

#include "enet_appmemutils_cfg.h"

#include "enet_apputils.h"

#define PKT_POOL_ENABLE 1U

/* ========================================================================== */

/* Structure Declarations */

/* ========================================================================== */

#if defined (ENET_SOC_HOSTPORT_DMA_TYPE_UDMA)

/* Enet UDMA DESC memories */

static EnetMem_DmaDescMemPoolEntry gDmaDescMemArray[(((16U) * ENET_CFG_TX_CHANNELS_NUM) +

((32U) * ENET_CFG_RX_FLOWS_NUM))]

__attribute__ ((aligned(ENETDMA_CACHELINE_ALIGNMENT),

section(".bss:ENET_DMA_DESC_MEMPOOL")));

/* RX & TX RingAcc memories */

static EnetMem_RingMemPoolEntry gRingMemArray[((2U) *

(ENET_CFG_TX_CHANNELS_NUM + ENET_CFG_RX_FLOWS_NUM))]

__attribute__ ((aligned(ENETDMA_CACHELINE_ALIGNMENT),

section(".bss:ENET_DMA_RING_MEMPOOL")));

#endif

#if (PKT_POOL_ENABLE == 1)

/* Eth packet info memory Q - large pool */

static EnetDma_Pkt gAppPktInfoMem_LargePool[(((32U) * ENET_CFG_RX_FLOWS_NUM) +

((16U) * ENET_CFG_TX_CHANNELS_NUM))];

/* Eth packet large pool memories */

static uint8_t gEthPktMem_LargePool[(((32U) * ENET_CFG_RX_FLOWS_NUM) +

((16U) * ENET_CFG_TX_CHANNELS_NUM))][ENET_MEM_LARGE_POOL_PKT_SIZE]

__attribute__ ((aligned(ENETDMA_CACHELINE_ALIGNMENT),

section(".bss:ENET_DMA_PKT_MEMPOOL")));

#endif

static const EnetMem_Cfg gEthMemCfg =

{

#if (PKT_POOL_ENABLE == 1)

.pktBufPool =

{

[ENET_MEM_POOLIDX_LARGE] =

{

.pktSize = ENET_MEM_LARGE_POOL_PKT_SIZE,

.numPkts = (((32U) * ENET_CFG_RX_FLOWS_NUM) +

((16U) * ENET_CFG_TX_CHANNELS_NUM)),

.pktInfoMem = gAppPktInfoMem_LargePool,

.pktInfoSize = sizeof(gAppPktInfoMem_LargePool),

.pktBufMem = &gEthPktMem_LargePool[0][0],

.pktBufSize = sizeof(gEthPktMem_LargePool),

},

},

#else

.pktBufPool =

{

[ENET_MEM_POOLIDX_LARGE] =

{

.pktSize = 0,

.numPkts = 0,

.pktInfoMem = NULL,

.pktInfoSize = 0,

.pktBufMem = NULL,

.pktBufSize = 0,

},

},

#endif

#if defined (ENET_SOC_HOSTPORT_DMA_TYPE_UDMA)

.ringMem =

{

.numRings = ((2U) *

(ENET_CFG_TX_CHANNELS_NUM + ENET_CFG_RX_FLOWS_NUM)),

.ringMemBase = gRingMemArray,

.ringMemSize = sizeof(gRingMemArray),

},

.dmaDescMem =

{

.numDesc = (((16U) * ENET_CFG_TX_CHANNELS_NUM) +

((32U) * ENET_CFG_RX_FLOWS_NUM)),

.descMemBase = gDmaDescMemArray,

.descMemSize = sizeof(gDmaDescMemArray),

},

#endif

};

const EnetMem_Cfg * EnetMem_getCfg(void)

{

return &gEthMemCfg;

}

/*

* PRUICSS

*/

/* PRUICSS HW attributes - provided by the driver */

extern PRUICSS_HwAttrs const gPruIcssHwAttrs_ICSSG1;

/* PRUICSS objects - initialized by the driver */

static PRUICSS_Object gPruIcssObjects[CONFIG_PRUICSS_NUM_INSTANCES];

/* PRUICSS driver configuration */

PRUICSS_Config gPruIcssConfig[CONFIG_PRUICSS_NUM_INSTANCES] =

{

{

.object = &gPruIcssObjects[CONFIG_PRU_ICSS0],

.hwAttrs = &gPruIcssHwAttrs_ICSSG1

},

};

uint32_t gPruIcssConfigNum = CONFIG_PRUICSS_NUM_INSTANCES;

/*

* UART

*/

/* UART atrributes */

static UART_Attrs gUartAttrs[CONFIG_UART_NUM_INSTANCES] =

{

{

.baseAddr = CSL_UART2_BASE,

.inputClkFreq = 48000000U,

},

};

/* UART objects - initialized by the driver */

static UART_Object gUartObjects[CONFIG_UART_NUM_INSTANCES];

/* UART driver configuration */

UART_Config gUartConfig[CONFIG_UART_NUM_INSTANCES] =

{

{

&gUartAttrs[CONFIG_UART_CONSOLE],

&gUartObjects[CONFIG_UART_CONSOLE],

},

};

uint32_t gUartConfigNum = CONFIG_UART_NUM_INSTANCES;

#include <drivers/uart/v0/dma/uart_dma.h>

UART_DmaConfig gUartDmaConfig[CONFIG_UART_NUM_DMA_INSTANCES] =

{

};

uint32_t gUartDmaConfigNum = CONFIG_UART_NUM_DMA_INSTANCES;

void Drivers_uartInit(void)

{

UART_init();

}

void Pinmux_init();

void PowerClock_init(void);

void PowerClock_deinit(void);

/*

* Common Functions

*/

void System_init(void)

{

/* DPL init sets up address transalation unit, on some CPUs this is needed

* to access SCICLIENT services, hence this needs to happen first

*/

Dpl_init();

/* We should do sciclient init before we enable power and clock to the peripherals */

/* SCICLIENT init */

{

int32_t retVal = SystemP_SUCCESS;

retVal = Sciclient_init(CSL_CORE_ID_R5FSS0_0);

DebugP_assertNoLog(SystemP_SUCCESS == retVal);

}

PowerClock_init();

/* Now we can do pinmux */

Pinmux_init();

/* finally we initialize all peripheral drivers */

I2C_init();

/* IPC Notify */

{

IpcNotify_Params notifyParams;

int32_t status;

/* initialize parameters to default */

IpcNotify_Params_init(¬ifyParams);

/* specify the core on which this API is called */

notifyParams.selfCoreId = CSL_CORE_ID_R5FSS0_0;

/* list the cores that will do IPC Notify with this core

* Make sure to NOT list 'self' core in the list below

*/

notifyParams.numCores = 4;

notifyParams.coreIdList[0] = CSL_CORE_ID_R5FSS0_1;

notifyParams.coreIdList[1] = CSL_CORE_ID_R5FSS1_0;

notifyParams.coreIdList[2] = CSL_CORE_ID_R5FSS1_1;

notifyParams.coreIdList[3] = CSL_CORE_ID_M4FSS0_0;

/* initialize the IPC Notify module */

status = IpcNotify_init(¬ifyParams);

DebugP_assert(status==SystemP_SUCCESS);

}

/* IPC RPMessage */

{

RPMessage_Params rpmsgParams;

int32_t status;

/* initialize parameters to default */

RPMessage_Params_init(&rpmsgParams);

/* VRING mapping from source core to destination core, '-1' means NO VRING,

r5fss0_0 => {"r5fss0_0":-1,"r5fss0_1":0,"r5fss1_0":1,"r5fss1_1":2,"m4fss0_0":3}

r5fss0_1 => {"r5fss0_0":4,"r5fss0_1":-1,"r5fss1_0":5,"r5fss1_1":6,"m4fss0_0":7}

r5fss1_0 => {"r5fss0_0":8,"r5fss0_1":9,"r5fss1_0":-1,"r5fss1_1":10,"m4fss0_0":11}

r5fss1_1 => {"r5fss0_0":12,"r5fss0_1":13,"r5fss1_0":14,"r5fss1_1":-1,"m4fss0_0":15}

m4fss0_0 => {"r5fss0_0":16,"r5fss0_1":17,"r5fss1_0":18,"r5fss1_1":19,"m4fss0_0":-1}

*/

/* TX VRINGs */

rpmsgParams.vringTxBaseAddr[CSL_CORE_ID_R5FSS0_1] = (uintptr_t)gRPMessageVringMem[0];

rpmsgParams.vringTxBaseAddr[CSL_CORE_ID_R5FSS1_0] = (uintptr_t)gRPMessageVringMem[1];

rpmsgParams.vringTxBaseAddr[CSL_CORE_ID_R5FSS1_1] = (uintptr_t)gRPMessageVringMem[2];

rpmsgParams.vringTxBaseAddr[CSL_CORE_ID_M4FSS0_0] = (uintptr_t)gRPMessageVringMem[3];

/* RX VRINGs */

rpmsgParams.vringRxBaseAddr[CSL_CORE_ID_R5FSS0_1] = (uintptr_t)gRPMessageVringMem[4];

rpmsgParams.vringRxBaseAddr[CSL_CORE_ID_R5FSS1_0] = (uintptr_t)gRPMessageVringMem[8];

rpmsgParams.vringRxBaseAddr[CSL_CORE_ID_R5FSS1_1] = (uintptr_t)gRPMessageVringMem[12];

rpmsgParams.vringRxBaseAddr[CSL_CORE_ID_M4FSS0_0] = (uintptr_t)gRPMessageVringMem[16];

/* Other VRING properties */

rpmsgParams.vringSize = IPC_RPMESSAGE_VRING_SIZE;

rpmsgParams.vringNumBuf = IPC_RPMESSAGE_NUM_VRING_BUF;

rpmsgParams.vringMsgSize = IPC_RPMESSAGE_MAX_VRING_BUF_SIZE;

/* initialize the IPC RP Message module */

status = RPMessage_init(&rpmsgParams);

DebugP_assert(status==SystemP_SUCCESS);

}

MMCSD_init();

PRUICSS_init();

/* PRU IEP Enable SYNC MODE */

CSL_REG32_WR(CSL_PRU_ICSSG1_PR1_CFG_SLV_BASE + CSL_ICSSCFG_IEPCLK, 1);

Drivers_uartInit();

}

void System_deinit(void)

{

I2C_deinit();

RPMessage_deInit();

IpcNotify_deInit();

MMCSD_deinit();

PRUICSS_deinit();

UART_deinit();

PowerClock_deinit();

/* SCICLIENT deinit */

{

int32_t retVal = SystemP_SUCCESS;

retVal = Sciclient_deinit();

DebugP_assertNoLog(SystemP_SUCCESS == retVal);

}

Dpl_deinit();

}

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/908/5633.example.syscfg

Thanks and Best Regards,

SI.