Hi,

Test the hardware of the motor drive board for us.

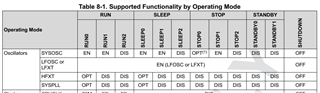

Use the Shutdown mode to measure the current 81uA, and the theoretical power consumption of the SHUTDOWN mode is 50nA, indicating that the peripheral hardware consumption is about 81uA.

The current measured current is 102uA using the Standby0 mode, indicating that the Standby0 mode is 21uA, which does not declare theoretical power consumption.

The current measured current is also 102uA using the Standby1 mode, indicating that the Standby1 mode is also 21uA, which is far greater than the theoretical value of 1.5uA.

What may be the reason for this? Is it possible that the chip is an old version of the old version. The chip measurement is a sample obtained before December 2022.

thanks in advace