Hi Team,

We are trying to make the Event trigger sub-system of the PWM channel to trigger 2 events on counter compare match :

- PWM interrupt AND

- ADC SoC

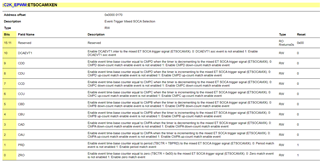

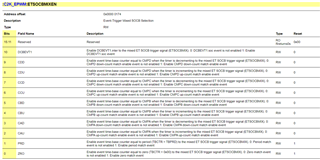

We have configured the ETSEL as below, to trigger the events, when the CMPA reg matches CNT reg; using the EPWM_Enable() API as in the Adc_app example app.

Expected behavior :

- Both the events should get triggered

- ADC conversion data should be parallelly available in the ADC_RESULTS register; when processing the PWM as high prio interrupt.

Observed behavior :

- PWM Cat0 and CAT2 ISR is working correctly when TBCNT counter reaches 0; and the ISRs are getting triggered. But this is happening independently; based on PWM_Init config.

- On configuring PWM module for multiple trigger using EPWM_Enable(); the PWM Cat0/CAT2 ISR does not operate at all.