Hello,

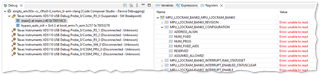

The debugger is unable to read the MPU registers. e.g. MPU_L2OCRAM_BANK0_PROGRAMMABLE_1_START_ADDRESS

Why is that please?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello Kier,

I was hoping to find some preliminary information for you on this but I was not able to and need to defer to our MPU expert who, as I mentioned on your other post regarding the MPU, is currently out of office. Sorry for the delay in support.

Best Regards,

Ralph Jacobi

Hi Kier,

It could be caused by one of the two following issues:

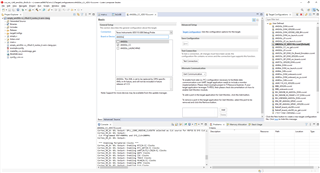

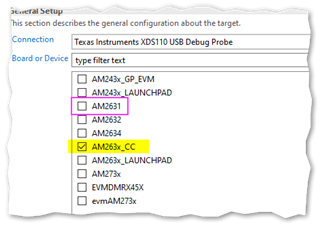

1. The incorrect CCXML:

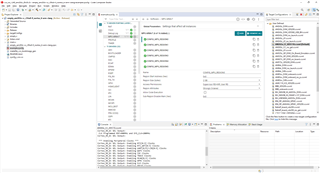

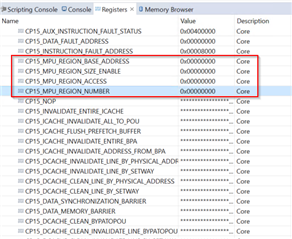

I am using the CCS 12.4.0 and AM263x CC with the above settings. The MPU registers look OK:

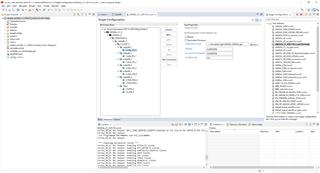

2. The incorrect MPU settings in example.syscfg:

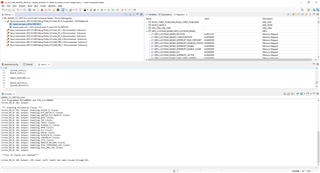

I am using the nortos empty project, the MPU registers look OK:

Best regards,

Ming

Hi Ming,

Thanks for the reply.

1. The incorrect CCXML:

Do you mean incorrect settings in the CCXML?

I started with the empty project. It contained AM2631.ccxml. This seemed reasonable to me but I changed the board selection to AM263x_CC like yours but this made no difference.

2. The incorrect MPU settings in example.syscfg:

I'm assuming the empty project from TI has the correct settings. How would I know I had incorrect settings if I cannot view the registers? Maybe I misunderstand your point.

Please find attached my empty project. Can you check if you can see the MPU registers with my project please? If so, then I would like help to debug why I cannot see the MPU registers on my PC/EVM board.

Hi Kier,

Can you share what is the logs for SOC ID parser script ?

Also what is the boot mode that you are using ?

Best Regards,

Aakash

Hi Aakash,

Also what is the boot mode that you are using ?

I'm using Dev Boot mode. Since I'm not using any kind of image, is the the first part of your request still relevant in this case?

Hi Aakash,

Sorry but I'm not familiar with UART boot mode.

Does it require connection via UART1? If so, I don't have a USB to UART cable with me. I'll have to try it when I'm in the office.

Hi Kier,

Please check this documentation - https://software-dl.ti.com/mcu-plus-sdk/esd/AM263X/latest/exports/docs/api_guide_am263x/EVM_SETUP_PAGE.html#BOOTMODE_UART to enable the UART boot mode and get the RBL meta data prints.

Best Regards,

Aakash

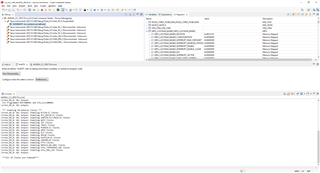

Hi Aakash,

The first attempt complained of "binascii.Error: Odd-length string" so I deleted character 'C' from Data.txt. The next attempt seemed to produce something which is attached.

--------------------------- SoC ID HW Info: --------------------------- partID : 0x0 partNumber : 0x2 PGVer : 0x2 ROMVer : 0x1 MetalVer : 0x0 --------------------------- SoC ID R5 ROM Info: --------------------------- r5 ROM Ver : 0x10000 --------------------------- SoC ID HSM Pub ROM Info: --------------------------- devName : AM263X������ devType : 0xabcd0004 --> HS_FS hsm ROM Ver : 0x10000 --------------------------- SoC ID HSM Sec ROM Info: --------------------------- Prime : 0x1 Key Rev : 0x0 Key Count : 0x0 SWRV SBL : 0x0 SWRV HSM : 0x0 TI MPK Hash : e7389b04c98dee79a00cfdeb879358c9a98fa3c9cf5150dfa0fed98a11af0f7ac149001816f5c2f2637f5d6fbd49f9348740823b62cc9d441db2fc70cd5b0ca6 Cust MPK Hash : 00000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000 Unique ID : 6793a51a6eca5b9b756d45b847eab1abf2e29a113d891deca6366d0f7bbba9f095db93dcf3bc2e471fa570104a89ddc79286d4aee52aad4276d4db4d0698a204

Hi Kier,

I take it your line of thinking is that MPU registers are masked due to some security setting that is local to my EVM?

This is correct.

The device you have is PGVer : 0x2 which is not supported for security hence you cannot use MPU Firewalls on this device. You need to get the PGVer : 0x3 or SR1.1 device of AM263x. Also you should be using SBLs instead of GELs which will load the TIFS firmware on the device in order to use the MPU features.

Best Regards,

Aakash

Thank you but this raises more questions than it answers.

1) So I can configure and use the MPU (through SYSCONFIG) but I can't monitor the MPU registers, is that correct?

2) Regarding "PGVer : 0x3" etc., how might I get these particular devices then? Are they available on a particular EVM that I can buy? More data required please.

3) Why doesn't the TRM mention any of this?

Hi Kier,

So I can configure and use the MPU (through SYSCONFIG) but I can't monitor the MPU registers, is that correct?

What you can configure via syscfg is ARMv7r MPU not the System MPU Firewall which is part of Security.

2) Regarding "PGVer : 0x3" etc., how might I get these particular devices then? Are they available on a particular EVM that I can buy? More data required please

Can you reach out to your TI representative ? In our current inventory, we have SR1.1 devices available and are ordered by default.

3) Why doesn't the TRM mention any of this?

System MPU Firewalls and its information are part of HSM Security Addendum, which is disclosed to customers after the NDA is in place. The access mechanism for the same is My Secure SW.

Best Regards,

Aakash

Hi Aakash,

The original question is to do with ARMv7r MPU. For some reason you've assumed the question is to do with System MPU Firewall.

My original post mentions MPU_L2OCRAM_BANK0_PROGRAMMABLE_1_START_ADDRESS. As you have confirmed, it can be configured with SYSCONFIG so what is the reason I cannot see it in the debugger?

Please confine your answer to ARMv7r MPU.

Hi Kier,

My original post mentions MPU_L2OCRAM_BANK0_PROGRAMMABLE_1_START_ADDRESS.

This is System MPU Firewall.

For ARMv7 MPUs, you need to check in the Core Registers.

Best Regards,

Aakash

Thanks for the clarification.

System MPU Firewalls and its information are part of HSM Security Addendum, which is disclosed to customers after the NDA is in place. The access mechanism for the same is My Secure SW.

It would save a lot of time if the TRM mentioned this in "3.8 Memory Protection Units (MPU)". Without it, the TRM gives the impression that these registers are accessible in the same way as any other.