Dear TI experts,

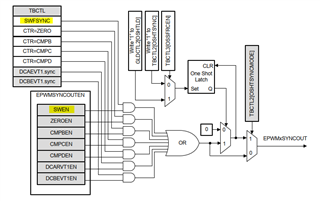

We want two channels of PWM starting Simultaneously without any delay.

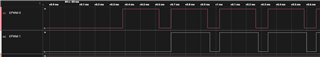

In the below snapshot: EPWM 0 starts first then starts the EPWM 1 but our application needs both PWM waves starting at same time.

Can you please suggest us how to configure both EPWM0 and EPWM1 pulses to start simultaneously at same time without any delay.