- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi

I am facing a issue when using safety library to execute SRAM_ECC_ERROR_FORCING_2BIT,SRAM_ECC_ERROR_FORCING_1BIT selft test.

This issue is only observed when application is combined with a boot loader application.

But if application run standalone then issue is not observed.

I need help to resolve this issue.

retVal = SL_SelfTest_SRAM(SRAM_ECC_ERROR_FORCING_2BIT, TRUE, &failInfoTCMRAM);

/* Run 1Bit ECC test on sRAM */

retVal = SL_SelfTest_SRAM(SRAM_ECC_ERROR_FORCING_1BIT, TRUE, &failInfoTCMRAM);

below is application link file configuration.

MEMORY

{

/* These configuration settings are required for all SafeRTOS based

* applications.

* If the whole build is using ARM mode then VECTORS length can be 0x20.

* When using thumb mode, 0x80 is required to accommodate the interwork

* code. */

VECTORS (X) : origin=0x00200000 length=0x00000080 vfill = 0xffffffff

KERN_FUNC (RX) : origin=0x00200080 length=0x0000ff80 vfill = 0xffffffff

FLASH0 (RX) : origin=0x00210000 length=0x001D0000 vfill = 0xffffffff

STACKS (RW) : origin=0x08000000 length=0x00003000

KERN_DATA (RW) : origin=0x08003000 length=0x00002000

RAM (RW) : origin=0x08005000 length=0x0007B000

ECC_VEC (R) : origin=0xf0400000 length=0x10 ECC={ input_range=VECTORS }

ECC_KERN (R) : origin=0xf0400000 + 0x10 length=0x1ff0 ECC={input_range=KERN_FUNC}

ECC_FLA0 (R) : origin=0xf0400000 + 0x10 + 0x1ff0 length=0x2e000 ECC={input_range=FLASH0}

}

ECC {

algoL2R5F021 : address_mask = 0xfffffff8 /* Address Bits 31:3 */

hamming_mask = R4 /* Use R4/R5 build in Mask */

parity_mask = 0x0c /* Set which ECC bits are Even and Odd parity */

mirroring = F021 /* RM57Lx and TMS570LCx are build in F021 */

}

/*----------------------------------------------------------------------------*/

/* Section Configuration */

SECTIONS

{

/* These configuration settings are required for all SafeRTOS based

* applications. */

/* The following symbols need to be exported:

*

* lnkKernelFuncStartAddr - the start of the Flash memory section used during runtime.

*

* IMPORTANT NOTE: lnkKernelFuncStartAddr can be relocated (e.g. when a

* bootloader is used), but it must be aligned according to its size

* (rounded up to the next power of 2), otherwise the MPU will be

* configured incorrectly.

*

* lnkEndFlashAddress - the end of the Flash memory section used during runtime.

*

* lnkKernelFuncStartAddr - the start address of the Flash block containing

* the interrupt vector table and the kernel functions.

* NOTE: This should be aligned according to the section size, i.e. 0x8000.

*

* lnkKernelFuncEndAddr - the end address of the Flash block containing

* the interrupt vector table and the kernel functions.

*

* lnkKernelDataStartAddr - the start address of the RAM block containing

* the system stacks and the kernel data.

*

* lnkKernelDataEndAddr - the end address of the RAM block containing

* the system stacks and the kernel data.

*/

/* On this demo application, the kernel functions section is placed at the

* start of the Flash memory; this will not be the case if the application is relocated. */

.intvecs palign(32), START( lnkStartFlashAddress ),START( lnkKernelFuncStartAddr )

fill =0xffffffff {} > VECTORS

.kernel_function END( lnkKernelFuncEndAddr ) :

{

*(KERNEL_FUNCTION)

} > KERN_FUNC

.unpriv_flash palign(32), END( lnkEndFlashAddress ) :

{

*(.text)

*(.const)

} > FLASH0

.cinit align(32) : {} > FLASH0

.pinit align(32) : {} > FLASH0

STACK_DATA START( lnkKernelDataStartAddr ) : {} > STACKS

KERNEL_DATA END( lnkKernelDataEndAddr ) : {} > KERN_DATA

.bss : {} > RAM

.data : {} > RAM

.sysmem : {} > RAM

LOG_DATA : > RAM //LOG

PROFILE_DATA : > RAM //PROFILE

/* These configuration settings are for the SafeRTOS TMS570LC43x FPU demonstration

* project. They are included as a demonstration of how task data can be

* grouped together into known locations, therefore enabling MPU regions to

* be defined. */

__idle_hook_data__

: START( lnkIdleTaskDataStartAddr )

{} > RAM palign( 0x20 )

}

Hi Vipin Kumar,

I am facing a issue when using safety library to execute SRAM_ECC_ERROR_FORCING_2BIT,SRAM_ECC_ERROR_FORCING_1BIT selft test.

This issue is only observed when application is combined with a boot loader application.

What is your exact issue, can you describe in more details. I mean is ESM flags are not setting after TEST? or is your code got stuck somewhere? or you are getting any aborts?

Please give me more details.

And also, if possible, can you please provide a simplest project for the issue?

--

Thanks & Regards,

Jagadish.

We had a meeting on Friday, and i should need to implement the error triggering at my end.

Hi Vipin Kumar,

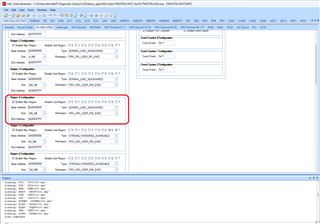

I understood the root cause of this issue, and it should be due to not enabling the SRAM ECC region in the MPU configurations something like as below:

If we didn't enable this region, then we can't read this region in our application and we can't alter the corresponding data.

So, it is very important to enable this region to force the SRAM ECC errors.

--

Thanks & regards,

Jagadish.

Hi Jagadish

I am unable to modify the region through HALGoGen.

is it required to do it manually.

with regards

Vipin Kumar

Hi Vipin Kumar,

Why you are unable to change from HALCoGen?

Try to change for application code, not for bootloader. If you enable the highlighted region for application then it should work.

--

Thanks & Regards,

Jagadish.

Hi Jagadish

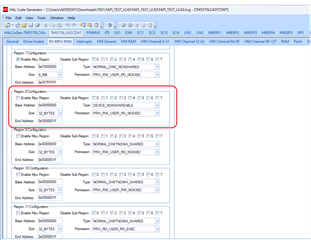

I attached the screenshot of application halcogen .

region 4 is already there but different address and i am not able to change it.

As I remember, I searched and found in the forum that it cannot be changed it, if application has any RTOS.

with regards

Vipin Kumar

Hi Vipin Kumar

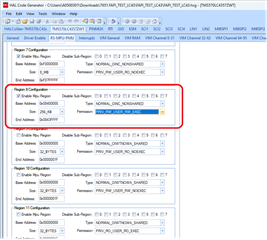

I added at region-4 but no need to be region-4.

Just select one not using region and there you can give the configuration.

For example region-8 is not using.

So, i can configure here as well:

--

Thanks & Regards,

Jagadish.