Hi,

this is my first time working with Sitara and posting a question here, so please bear with me if the question seems somewhat unusual :)

I have occasional I2C bus hanging due to arbitration loss after an "ungraceful" reset. How can I address this?

Before initiating any I2C communication, I call the Cdd_I2c_Init function. However, due to the design, it's impossible to call Cdd_I2c_DeInit before a "warm-start" reset.

I'm using the MCAL Version AM263x 08.06.02, and I'm utilizing the Cdd_I2c Driver included in that package.

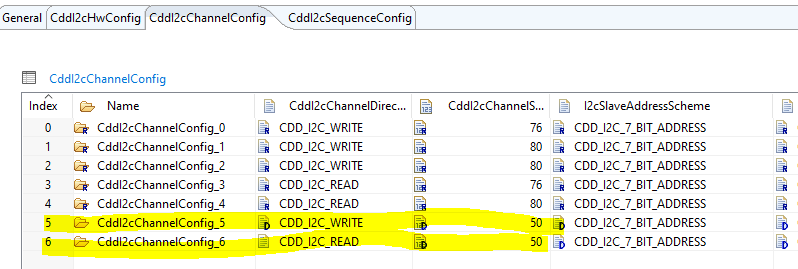

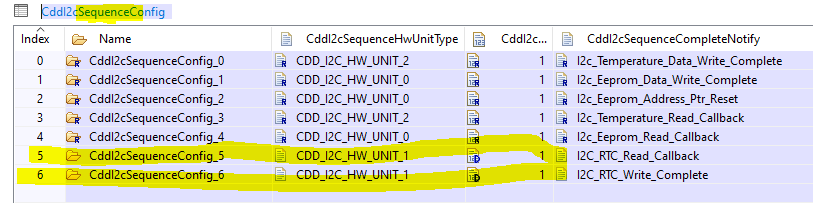

As a workaround, I modified the startup sequence to run Cdd_I2c_Init, Cdd_I2c_DeInit, and then Cdd_I2c_Init again to reset the I2C peripheral. This approach has somewhat helped, but I'm still facing issues with the bus hanging. To address the remaining hanging issues, I set the CddI2cArbitrationLossParam variable to CDD_I2C_RECURRENT_MODE, aiming to send 9 clock pulses to the slave to synchronize the bus - but this hasn't been effective.

Of course, there might be issues with the target I'm communicating with, but do you have any suggestions on what I can do from the microcontroller side to resolve the I2C bus hanging, despite resetting the I2C peripheral and using CDD_I2C_RECURRENT_MODE?

Additionally, I'm using the I2C1 instance in polling mode and running the communication at a 100KHz bitrate.

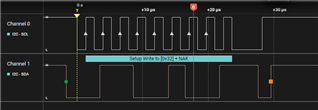

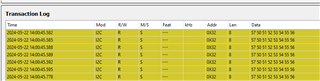

Moreover, in Code Composer, I see the hang in Cdd_I2c_Polling_Mode_Receive, specifically in the while loop on line 509. The IsrStatus variable holds the value 400h.

Any suggestions for improving the implementation are most welcome.

Many thanks,

Mikael