Other Parts Discussed in Thread: SYSCONFIG

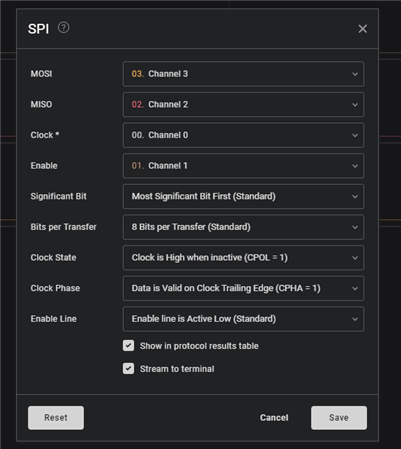

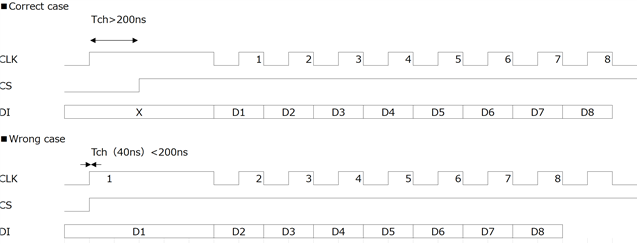

I am using MCSPI with MODE 3.

1.How can the results of setting POL and PHA for MCSPI_CHCONF_0/1/2/3[1],[2] be reflected in the output?

Currently, just setting POL=1 and PHA=1 does not make SPI_CLK high.

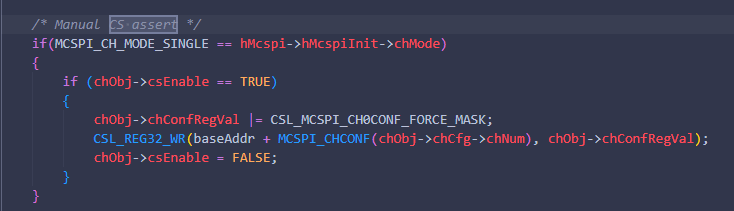

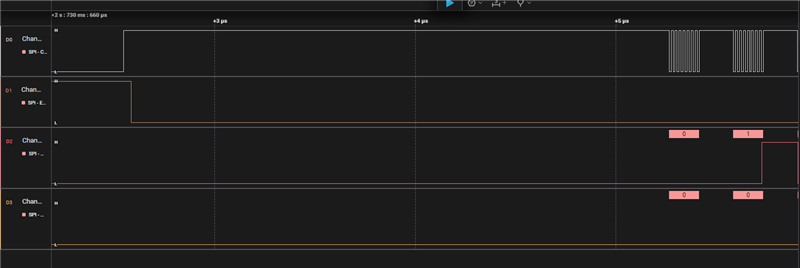

After that, SPI communication is performed (MCSPI_CHCONF register FORCE=1), SPI_CLK goes high and operation starts.

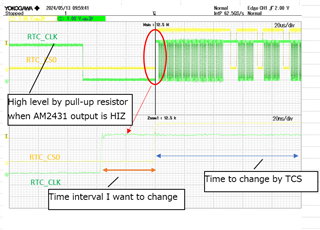

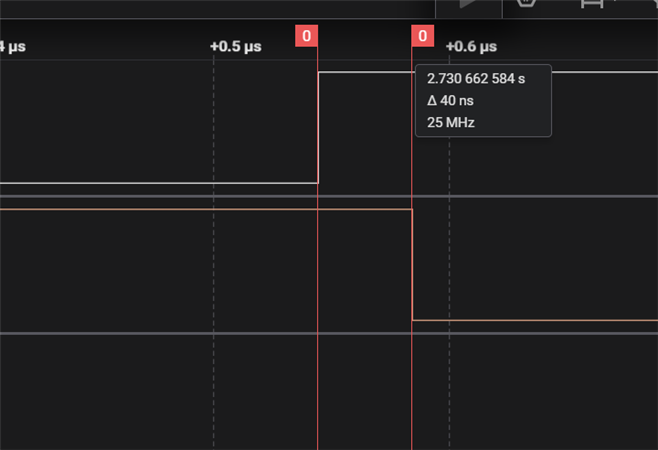

At this time, the time between the rising edge of SPI_CLK and the assertion edge of SPI_CS is too short to meet the hold time of the external SPI device.

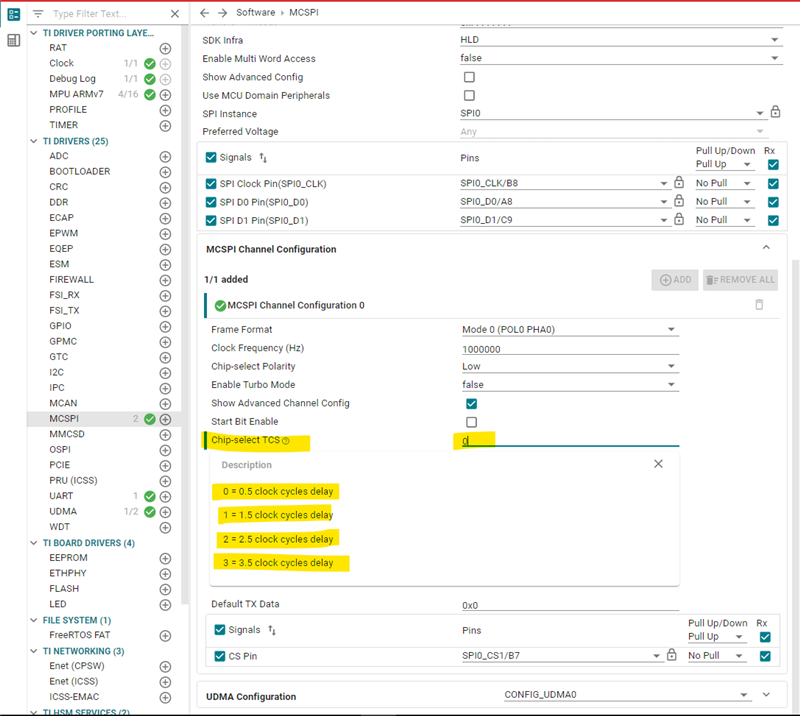

2. How can the time between the rising edge of SPI_CLK and the assertion edge of SPI_CS be increased?