Part Number: TMS570LC4357

Tool/software:

Here i am listing out the all the bugs in the Cyclic Redundancy Check (CRC) Controller Module for both little endian (e.g. RM57Lx) and big endian (e.g. TMS570LC43x) devices of Hercules family.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TMS570LC4357

Tool/software:

Here i am listing out the all the bugs in the Cyclic Redundancy Check (CRC) Controller Module for both little endian (e.g. RM57Lx) and big endian (e.g. TMS570LC43x) devices of Hercules family.

Issue-1:

64-bit data will not get copy properly to the Signature or CRC Value registers in big-endian devices (TMS570LC43x):

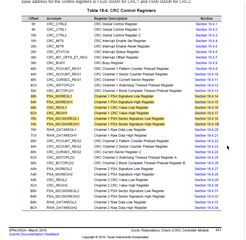

If you see the order of the lower register and higher registers in both big-endian and little-endian devices.

Lower registers are at lower address and followed by higher registers are at higher address. Example CRC_REGL1 at 68h offset and CRC_REGH1 at 6Ch offset.

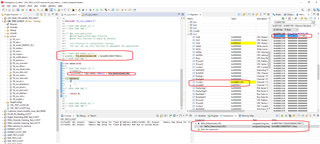

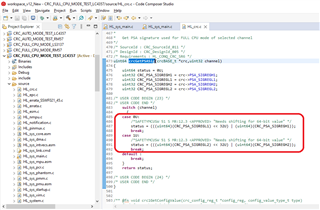

For example, if you see the below picture:

Here i am trying to copy the 0xAABBCCDDEEFF0011 to the CRC value register in 64-bit mode for big endian devices, if you verify carefully my higher data word 0xAABBCCDD was copied to the CRC_REGL1 and lower data word 0xEEFF0011 was copied to the CRC_REGH1 register.

But we expect it should be reverse that is lower data word to the lower register and higher data word to the higher register right. So, in big-endian devices whenever you are trying to move data to these registers using either DMA or directly then the input data must be swap (lower 32bit with higher 32bit).

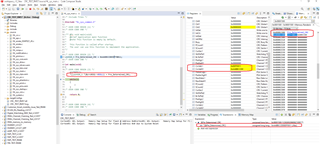

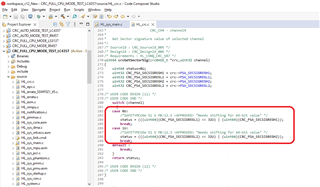

If you verify same testing for a little-endian device (e.g. RM57Lx):

As you can see the data moved correctly, that is lower word (0xEEFF0011) of 64-bit data moved into the lower register CRC_REGL1 and higher word (0xAABBCCDD) was moved into the higher register CRC_REGL1.

So, in little-endian device we no need to swap the data before writing into above registers.

Conclusion:

In big-endian devices (e.g. TMS570LC43x) for AUTO mode or Semi-CPU mode before you are going to give data to the DMA each 64-bit word in the corresponding data should need to swap (lower and higher 32bit words) before DMA starts copying the data to the PSA signature registers / CRC value registers.

In big-endian devices (e.g. TMS570LC43x) for Full-CPU mode, before giving data to the crcSignGen API each 64-bit word in the corresponding data should need to swap (lower and higher 32bit words).

And this is not required for little endian devices (e.g. RM57Lx).

For more details refer attached examples.

Issue-2:

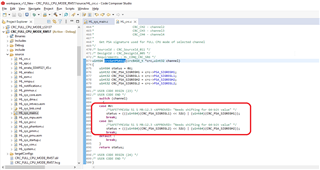

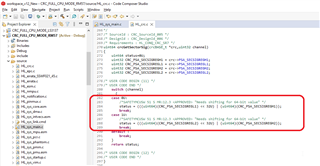

crcGetSectorSig and crcGetPSASig API's in the CRC driver are wrongly returning the compressed signatures in both little-endian and big-endian devices:

If you verify the definitions of these functions in drivers for both TMS570LC43x and RM57Lx:

While just before returning the compressed CRC by these functions, they are shifting lower register to the higher 32bit value and higher register to the lower 32bit value. This should not be correct the higher register value should be at the higher 32bit of the 64bit value and lower register value should be at the lower 32bit of the 64bit value.

Conclusion:

In Auto mode anyway these functions are not required because CPU no need to read and compare the compressed signature.

If you are using these API's in Semi-CPU or Full-CPU modes, after getting 64-bit value from these functions the corresponding value should need to be swap before using it.

For more details refer attached examples.

Examples:

You can find examples for all the modes (Auto, Semi-CPU and Full-CPU) for both little- and big-endian devices (TMS570LCx and RM57Lx) in below FAQ: