- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Primary Boot Mode:SPI

Backup Boot Mode: UART

SDK: mcu_plus_sdk_am243x_09_00_00_35

We made a sbl_ospi.release.hs_fs.tiimage for the custom flash, the board can load the application correctly and run when it is powered on,

but when I do a warm reset or system reset, it will jump to uart boot, what is the cause of this?

power on:

Bootloader_open bootHandle=1879120384

Bootloader_parseMultiCoreAppImage status=0, offset=32

Bootloader_loadCpu CSL_CORE_ID_R5FSS0_0 isSelfBoot=1

[BOOTLOADER_PROFILE] Boot Media : NOR SPI FLASH

[BOOTLOADER_PROFILE] Boot Media Clock : 133.333 MHz

[BOOTLOADER_PROFILE] Boot Image Size : 0 KB

[BOOTLOADER_PROFILE] Cores present :

r5f0-0

[BOOTLOADER PROFILE] SYSFW init : 12165us

[BOOTLOADER PROFILE] System_init : 19368us

[BOOTLOADER PROFILE] Drivers_open : 277us

[BOOTLOADER PROFILE] Board_driversOpen : 482us

[BOOTLOADER PROFILE] Sciclient Get Version : 1490us

[BOOTLOADER PROFILE] CPU load : 9778us

[BOOTLOADER_PROFILE] SBL Total Time Taken : 43563us

Image loading done, switching to application ...

CSL_CORE_ID_R5FSS0_0:Image loading start ...

CSL_CORE_ID_R5FSS0_0:Image loading done, offset=32, Image size=2801632

\ | /

- RT - Thread Secure AUTO based on 4.1.1-LTS

........

after warm reset:

02000000011a0000616d3634780000000000000048534653000002000000020002a6000000000000b018658ad99dc903c8c9bfb27b12751099920a042ad1dfea7b7ba57369f15546de285edde6a7b39a8bdc40a27b237f8fb1e57f245e80b929c1e28b024aa2ecc6ad0bc40b00000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000007e893d3d4adf9f7869147dde82b135ac31a9bab04e85a8cb67713754e961515CCCCCCCCCCCCCCCCCCCC

Thanks for you reply,The moment we do doing the warm reset at the time of simulation is uncertain and the warm-reset function at runtime is called directly via the RTOS shell.

Hello,

What is the exact SPI primary bootmode you are using?

I am suspecting the ROM is having trouble reading the flash after a warm reset. This may happen if the flash is not getting reset on wam reset and so the ROM gets the flash part in the state left by the bootloader.

Regards,

Prashant

Hello,

We configure bootmode to bit[15:7] = [0000 1101 0] ,bit[6:0] = [001 1011], so our primary bootmode is SPI.

The flash we use is GD25Q256 and the communication protocol is 1s-1s-1s,PHY MODE is not enable, Once this mode is used, an error occurs when the SPI communicates with Flash.

In the past few days, we've tried to configure flash's reset function, but it didn't work. why RESETSTATz can't produce a reset signal to #RESET of flash?

I found that the EVM board OSPI (8d-8d-8d) can reset the flash, but my board can't generate a reset signal using 1s-1s-1s.

Do you have any other suggestions?

Best wishes

Hello,

How is the RESET pin of flash in handled in your board schematics?

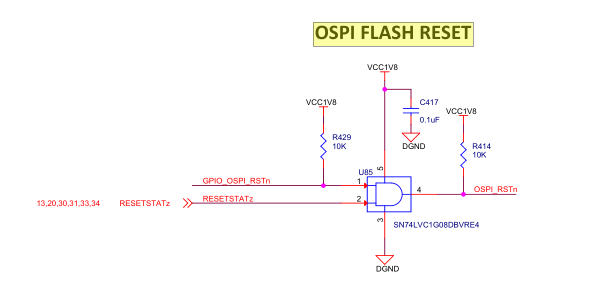

This is the schematics on the TMDS243EVM

On another note, have you tried software flash reset just before triggering the warm reset?

Regards,

Prashant

Hello,

Finally, we solved this problem by modifying the warm reset signal(RESETSTATz).

The cause of the problem is indeed the processing of the flash reset pin, and the flash reset pin has other functions on our board to be multiplexed..

But I have a question is that the reset signal (GPIO_OSPI_RSTn) of the OSPI must be in 8D-8D-8D mode to be generated? This signal was not measured on our board [1S-1S-1S].

Best wishes

Hello Pan Fei,

GPIO_OSPI_RSTn is an alternative reset option that can be used to reset the flash without resetting the SOC.

GPIO_OSPI_RSTn is connected to one of the SOC IO for software control of flash reset.

Finally, we solved this problem by modifying the warm reset signal(RESETSTATz).

The cause of the problem is indeed the processing of the flash reset pin, and the flash reset pin has other functions on our board to be multiplexed.

Are you able to share the schematics to review and comment.

Is there a pullup connected to the flash reset input.

If yes you may have to reconfigure the pullup to pulldown to hold the flash in reset until the SOC reset status is de-asserted.

Regards,

Sreenivasa

Hello Sreenivasa,

The flash in my board is selected to be GD25Q256 with WSON8 package, the reset pin is the hold function by default, it needs to be configured as the reset function through the status register,and the QUAD mode cannot be used, otherwise, this pin will become the data pin of quad communicatio, The above two points are the main reasons why the warm reset goes into UARTmode.

Secondly, my board has a 3.3V pull-up with 10K on RESETSTATz, at first we thought there was a problem with this, we changed it to a pull-down, but later we found that the other board with pull-up also succeeded.

The schematic is the same as the EVM board except for the pull-up.

Best regards

Panfei

Hello Pan Fei,

Thank you for the *inputs and appreciated.

Please note that having a pullup on the reset pin enables the flash during power-up.

You may not be seeing a functional issue but this could affect the flash performance.

Regards,

Sreenivasa

Hello,

Thank you for the reminder, we'll pay attention to this later.

Regards,

Panfei