Other Parts Discussed in Thread: AM2634

Tool/software:

I am currently using the AM2634 development board and working with the MCAL CAN module. Initially, I used polling mode, and it worked without issues. Later, I wanted to try interrupt mode, but after executing the following code to send data, it only successfully sends data the first time and cannot enter the interrupt handler. Could you please help me identify what might be missing in my configuration? Thank you.

Additionally, I am using the MCAL version MCAL_AM263X_10.00.00.

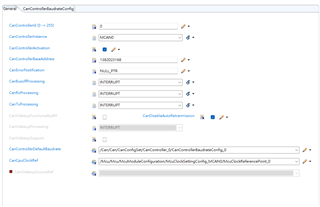

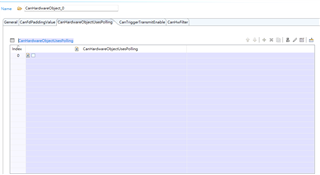

The configuration of MCAN is shown below.

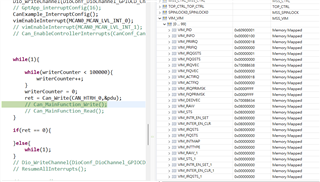

Here is my code:

void CanExample_InterruptConfig(void)

{

vimInit();

Vim_IntCfg Can_IntCfg;

Can_IntCfg.map = VIM_INTTYPE_IRQ;

Can_IntCfg.type = VIM_INTTRIGTYPE_LEVEL;

Can_IntCfg.intNum = MCAN0_MCAN_LVL_INT_0;

Can_IntCfg.intNum = MCAN0_MCAN_LVL_INT_0;

Can_IntCfg.handler = Can_0_Int0ISR;

Can_IntCfg.priority = VIM_PRIORITY_0;

vimRegisterInterrupt(&Can_IntCfg);

}

Mcu_Init(&McuModuleConfiguration);

Mcu_InitClock(McuConf_McuClockSettingConfig_McuClockSettingConfig_MCAN0);

while ( MCU_PLL_LOCKED != Mcu_GetPllStatus() )

{

/* wait until all enabled PLLs are locked */

}

Mcu_DistributePllClock();

Port_Init(&PortConfigSet_0);

Can_Init(&CanConfigSet);

Can_SetControllerMode(0, CAN_CS_STARTED);

CanExample_InterruptConfig();

vimEnableInterrupt(MCAN0_MCAN_LVL_INT_0);

// Send data

while(1){

while(writerCounter < 100000){

writerCounter++;

}

writerCounter = 0;

ret = Can_Write(CAN_HTRH_0,&pdu);

}

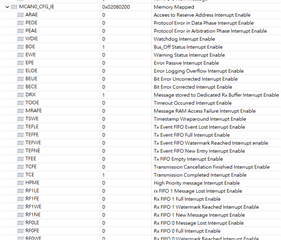

Additionally, I have included some register values during runtime. It appears that the MCAN interrupt is enabled and gets triggered.