- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

Tool/software:

Hi team,

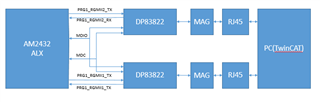

I'm currently working with AM2432 + DP83822 PHY for Industrial communication

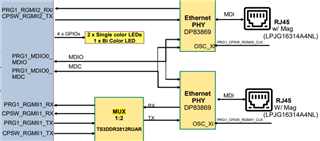

This custom board was designed by taking AM243 LP as reference.

In LP, MUX IC was connected between SoC and DP83869 in PHY 1 side for selection between CPSW and PRG lines.

MUX_SEL pin is configured pulled high and low based on the requirement.

As per requirement, we have removed the MUX IC and have taken PRG1_RGMII1 lines connected directly from SoC to PHY 1

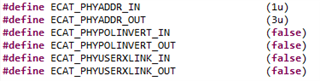

EtherCAT Slave simple demo code uses PRG1 lines for communication(MUX SEL was not configured and it was pulled low by default) and currently we are using same for testing with DP83822 driver.

PHY 2 is connected with PC(TwinCAT - EtherCAT protocol) and working fine.

I'm having Issues connecting PC(TwinCAT - EtherCAT protocol) with PHY1.

I tried different configuration for custom board and got PHY2 working after the below configurations

Is MUX removal a issue? Do I need to configure anything in software for MUX removal in EtherCAT slave simple demo code?

Regards,

D. Jenita

Hello Jenita

Thank you for the query.

Would you be able to share the customer board schematics to do a quick check.

I amy have to reassign to the software expert after review if the issue observed is not related to hardware.

Regards,

Sreenivasa

Hi Sreenivasa,

Please find the PHY section schematics below

Regards,

Chockalingam

Hello Chockalingam

Thank you.

I need a searcheable PDF to review.

Regards,

Sreenivasa

Hi ,

Could we have a private chat to provide the entire schematic, or could you kindly share your mail ID?

Regards,

Chockalingam

Hello Chockalingam

Thank you.

Please send over private chat.

Regards,

Sreenivasa

Did you received my files in private chat, Pls acknowledge here.

Regards,

Chockalingam

Hello Chockalingam

Thank you for checking.

I received the schematics.

Allow me few days to review.

Regards,

Sreenivasa

Hello Chockalingam

Thank you. Will update you when i have some observations or queries.

Regards,

Sreenivasa