Hello Support,

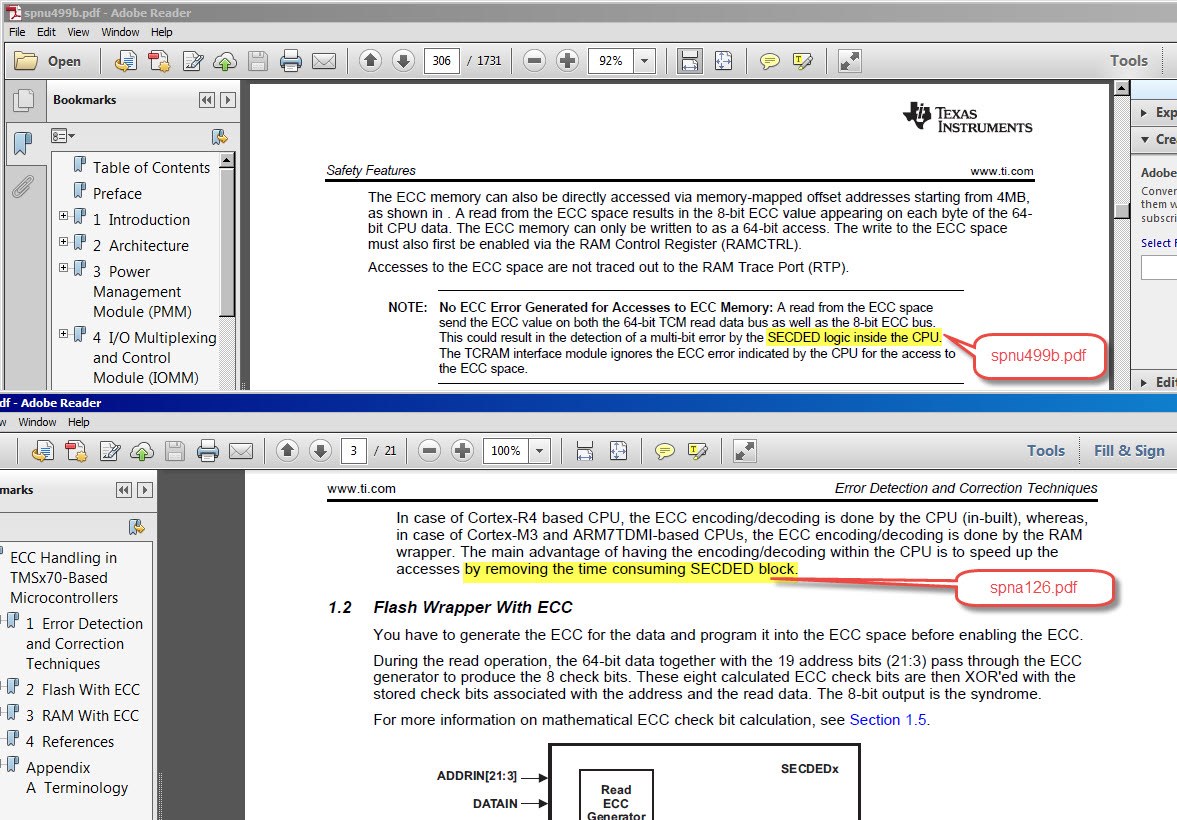

In the spna126.pdf it is mentioned that ECC encoding/decoding logic is resident with Cortex-R4 side and "time consuming SECDED Logic is in the Flash Wrapper".

In spnu499b.pdf, it is mentioned that SECDED Logic is inside Cortex-R4.

I have attached the following snippets from the above mentioned document for easier reference.

Can you please explain ECC complete signal chain is divided between Flash Wrapper side and Cortex-R4 side?

I am assuming it consists of following sub-blocks:

ECC Encoding Logic -- For k bit data it produces n-k bits of ECC

ECC Decoding Logic -- For n bit input, it calculates n-k bits of ECC

SECDED Logic for Error Detection -- Detects if there is more than one bit error and if it is only one bit error then it corrects it

Thank you.

Regards

Pashan