Other Parts Discussed in Thread: EK-TM4C1294XL

Daniel Vamos said:I have code which based on clock functions (ADC related stuff) and I didn't find any Timer example in the RTOS package

Hi Daniel,

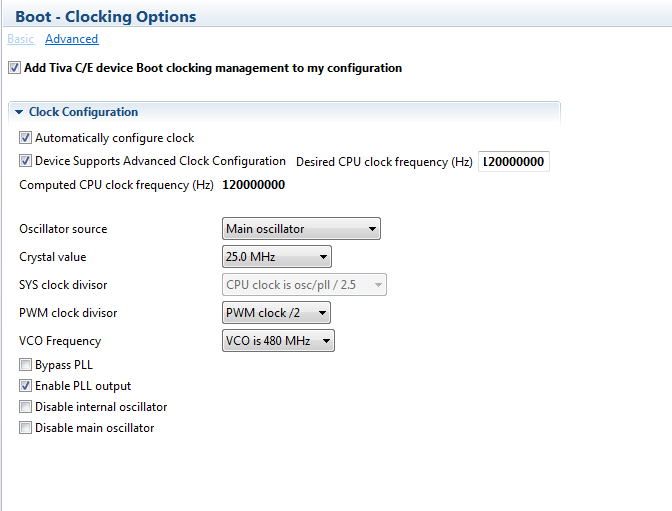

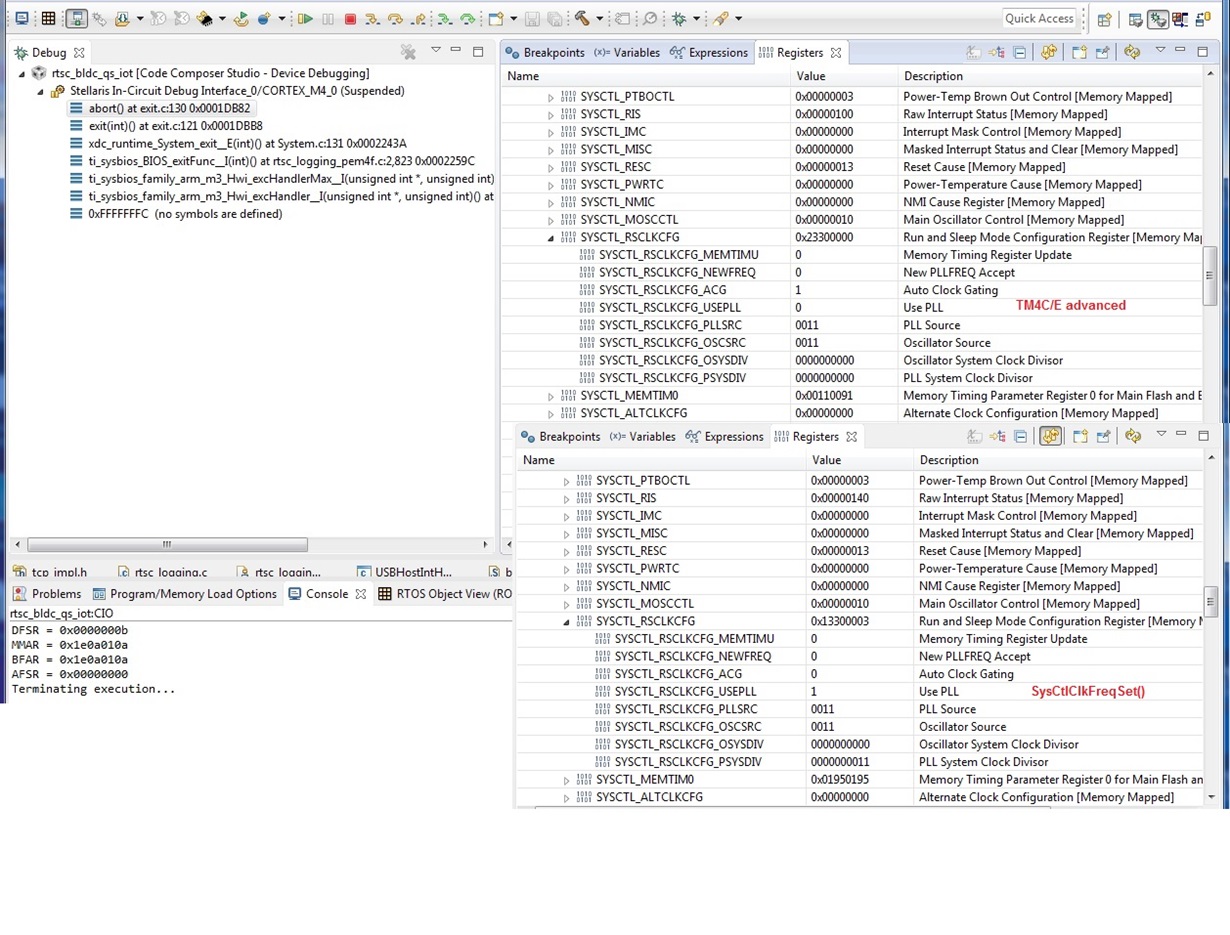

We have several ADC sequencer samples @2MSPS rate that required PLL divisor be properly configured for SYSCLK 120Mhz. That said and with great regret the latest TI-RTOS Boot module failed to achieve any such goal. Fact is the TivaC/E advanced clocking in Boot module was disabled for proper ADC clock speeds to occur using Tivaware SysCtlClkFreqSet(). Oddly ROV Boot shows output PLL=false yet the ADC and EMAC PHY run at the correct clocking speed. We could not get RTOS TM4C Advanced Clocking by itself to execute the application without quickly faulting after POR. The application seems to execute in slow motion prior to faulting.

Something is not working well in Boot modules TM4C Advanced clock transition from PIOSC into MOSC, no matter if PSYSDIV (SYSDIV) is made 2 or 2.5 as typical setting.

Best of luck to you.