Other Parts Discussed in Thread: LAUNCHXL-F280049C, MOTORWARE, C2000WARE

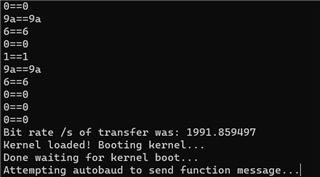

I'm trying to get the serial flash programmer to work on custom firmware with a F280041C. The kernel successfully loads on the device before flashing custom firmware. The program stops at the attempting autobaud message.

The command I am using is this:

serial_flash_programmer.exe -d f28004x -k C:\ti\c2000\C2000Ware_5_01_00_00\utilities\flash_programmers\serial_flash_programmer\f28004x_fw_upgrade_example\flashapi_ex2_sci_kernel.txt -a C:\ti\c2000\C2000Ware_5_01_00_00\utilities\flash_programmers\serial_flash_programmer\f28004x_fw_upgrade_example\led_ex1_blinky.txt -p COM5 -v

I tried getting the LAUNCHXL-F280049C to replicate the issue, but the device successfully locks with the autobaud and the DFU process works fine. I can also flash my custom firmware .txt file.

I recompiled the flashapi_ex2_sci_kernel project in CCS studio and it works on the LAUNCHX-F280049C (CPU1_RAM is the only build target that would work on the LAUNCHXL-F280049C), but still crashes at autobaud on my hardware.

I have checked that the device is booting into SCI and that the SCI Pins are defaults 28 and 29. I don't think the kernel would be able to load to the device if it wasn't in the SCI bootmode, is this correct?

Could the problem be caused by the difference in flash size between the 2 devices? F280049C is 256KB while F280041C is 128KB.

Could this require a change to the 28004x_generic_ram_lnk.cmd in the Kernel project?

The custom hardware for the SCI port and SCI bootmode settings are nearly identical to the LAUNCHXL-F280049C, so I don't think it is a hardware problem but I haven't ruled that out completely.

Thanks,

James