Tool/software:

Hi Expert

Customer developing OBC DCDC with our F280039, the MCU controls PFC and CLLLC in the OBC power stage.

The PFC control frequency is 30KHz, customer find if the control ISR run in CPU the PWM CMP data cannot be updated in 33.3us (actual time ~36.5us). but CLA can finish the ISR in ~27us.

We did the check below:

The Processor Option shown below, FPU/ TMU is enabled:

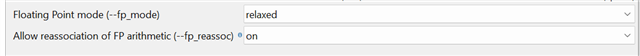

The Optimization shown below, floating point mode is relax, which allow compiler to replace the math.h sin/cos to TMU __sin/ __cos

The assembly of CPU is shown below:

The assembly of CLA is shown below:

The instructions in control ISR are "if else branch" / "+ "/ "-" / ''/" / "sin"/ "cos".

All variables are write with F suffix, for example, 2.0 write as "2.0f".

Is there any other actions I can take to optimize the code?

Thanks

Joe