Tool/software: Code Composer Studio

Hi,

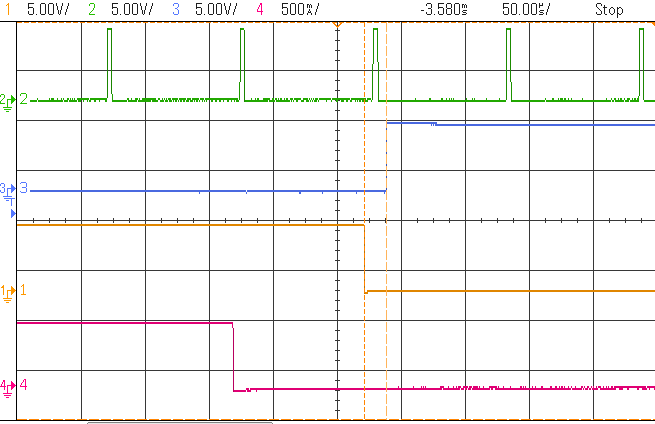

I observe that when I'm loading the CMPA register with the desired variable for EPWM comparison, the delay in the falling edge is more than that in the rising edge. The pink line is the variable that I'm feeding to CMP register, it's low value is 0 and high is 1.2*TBPRD. Hence I expect the output waveform of EPWM (yellow) to closely follow the input pink waveform, which I'm displaying using a DAC. The green pulses indicate the zero crossings of TBCTR up down counter, being displayed as the EPWM output by comparing against 0.1*TBPRD.

(please ignore the cursors (dotted vertical lines) in the following figures, by 'delay' I mean the lag between the pink and the yellow waveforms rising/falling')

Rising edge: delay less than one period of TBCTR triangle

Falling edge: delay is one period of TBCTR triangle

Due to this increased delay in the falling pulse in comparison to that of the rising pulse, the width of the output pulses is greater than that of the input variable pulse. This is the case irrespective of whether the shadow is enabled or not.

How do I minimize the delay of the EPWM output pulses, so that the lag between the pink and yellow waveforms is minimized?

How do I ensure that the delay is the same for both edges, so that the pulse widths are unaffected?

Thanks

Archana