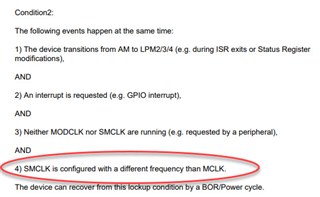

Regarding Errata PMM32

We are a little concerned for condition 2, but are hoping that we are saved by the 4th requirement.

We are running SMCLK with the same source as MCLK, but divided by 4.

DCOCLK = 8MHz

MCLK = DCOCLK / 1

SMCLK = DCOCLK / 4

Do we have a problem?