Hello,

I am trying to run two timers: TimerA and TimerB for pwm generation simultaneously.

Timer A : clock source is TACLK using external crystal of 16MHz (provided from pin 3.4 of another msp430fr5969 having populated Y1 with 16 MHz crystal)

Timer B: clock source is SMCLK which is mapped to MCLK at 16 MHZ (DCO source)

My final aim is to generate 2FSK signal at high baudrates for that I am using timer A as my baudrate source and Timer B to generate 2 frequencies of FSK

Relevant code snippets:

void set_cpu_freq() {

FRCTL0 = FRCTLPW | NWAITS_1;

CSCTL0_H = CSKEY >> 8; // Unlock CS registers

CSCTL1 = DCORSEL | DCOFSEL_4; // Set DCO to 8MHz

CSCTL2 = SELA__VLOCLK | SELS__DCOCLK | SELM__DCOCLK;

CSCTL3 = DIVA__1 | DIVS__1 | DIVM__1; // Set all dividers to 1

}

int main(void) {

WDTCTL = WDTPW | WDTHOLD; // Stop watchdog timer

P1OUT &= ~BIT3; // Clear P1.0 output latch for a defined power-on state

P1DIR |= BIT3; // Set P1.0 to output direction

P1DIR &= ~BIT2;

PM5CTL0 &= ~LOCKLPM5; // Disable the GPIO power-on default high-impedance mode

// to activate previously configured port settings

set_cpu_freq();

while (1) {

//message generation code: generates an array with binary information

__enable_interrupt();

TA0CTL = TASSEL__TACLK | MC_1 | TACLR; // SMCLK, Up mode, no divider

TA0CCR0 = (16000000/10000) - 1; // Set period based on SMCLK frequency

TA0CCTL0 = CCIE; // Enable interrupts

TA0CCTL1 = OUTMOD_7;

TB0CTL = TBSSEL__SMCLK | TBCLR | MC_1 ; // SMCLK, up mode, /8 divider

TB0CCTL1 = OUTMOD_7;

TB0CCTL0 = CCIE; // Enable CCR0 interrupt

delay_ms(100);

}

}

#pragma vector=TIMER0_B0_VECTOR

__interrupt void Timer0_B0 (void)

{

P1OUT ^= BIT3; // Generates the FSK frequency

}

__attribute__((interrupt(TIMER0_A0_VECTOR))) //controls the baud rate of the FSK signal

void timer_a0_isr(void) {

if (tx_counter < TXLEN){

if (arr[tx_counter] == 0){

TB0CCR0 = (CPU_FREQ/(2*300000)) -1;

}

else if(arr[tx_counter] == 1){

TB0CCR0 = (CPU_FREQ/(2*400000)) -1;

}

tx_counter++;

}

else{

tx_counter = 0;

disable_signal();

msp430_timer_stop();

}

}

Problem:

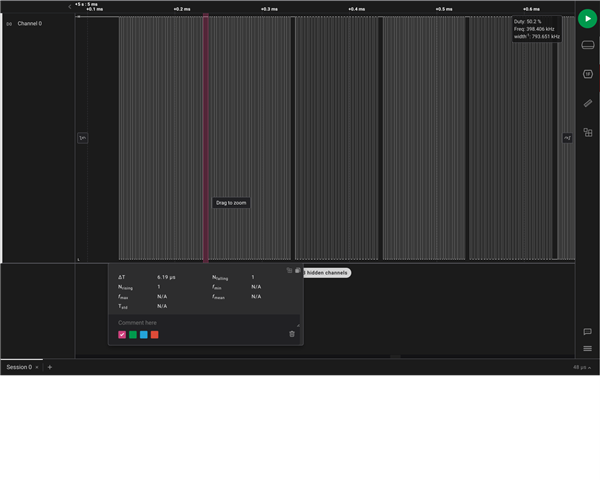

As depicted in the below image, I observed delays of about 6-7 microseconds between frequency switches, initially I was using SMCLK for both of the Timers A and B, observing the same issue, I assumed this must be an issue originating from the fact that both the timers using same source i.e SMCLK, I switched to the current setup of using TACLK for Timer A annd SMCLK for Timer B but the same issue persists, resulting in limitations of baudrate as the 6-7 microsecond gap becomes much more significant as I increase the baudrate eg 30kbps. My aim is to have atleast 100Kbps of baudrate.

Anticipating some suggestions from the community to mitigate this issue.

Regards!