Other Parts Discussed in Thread: PGA302, , ENERGIA, USB2ANY, PGA305, INA128

I'm trying to configure PGA302(slave) using MSP430FR5969 (master) launchpad through I2C protocol. I want to set the P Gain so the input voltage is amplified according to the gain. I'm giving input voltage to VINPP and VINPN pins and checking the output on Vout terminal. I have connected P1.6 (SDA) to pin 13 and P1.7 (SCL) to pin 14. I'm giving VDD of 5V to PGA302. I have grounded the VINTP and VINTN.I have connected common ground to both the devices.

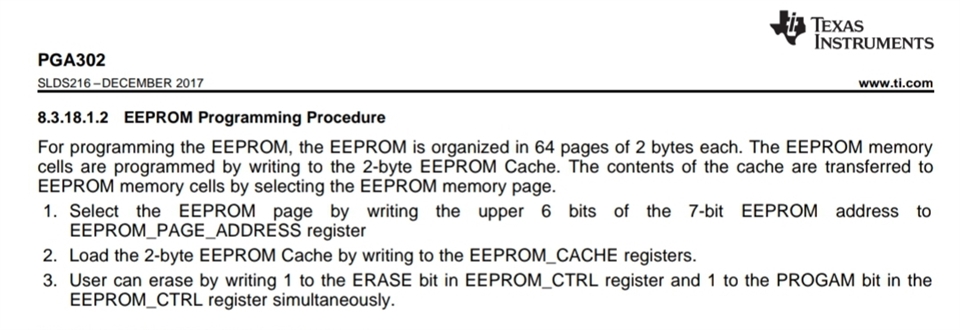

In the CCS code, I am putting the PGA302 in reset mode by sending 0x03 to register address 0x0C of slave address 0x40. Then I set the P gain by sending 0x01(for gain of 2 V/V). And finally I take out the slave from reset mode by sending 0x00 to register address 0x0C of slave address 0x40. I am using the polling mode(checking the flag is cleared for Tx buffer to be ready).

I'm unable to view the waveform of SDA and SCL in oscilloscope. Differing the P Gain Value doesn't change the Vout value. I can see the TXBUF is getting the values I'm sending, so I assume the slave is responding.

Am I missing some steps or is there an issue with the connection? If possible please provide a sample code for I2C communication of MSP430FR5969 to set the P Gain of PGA302.