Part Number: MSP430FR6928

Other Parts Discussed in Thread: MSP430FR6989

I tried to post this as a Code Composer Studio issue but I was brought to this forum

I wrote an application where I collect data from different sources (e.g. a2d, timer calculations, etc.) and I place the collected data as an object of a structure. Then I create an array of these structures.

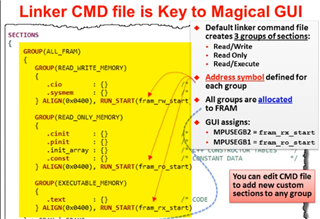

I'm using an MSP430FR6928. For starters, the array had about 100 objects. The linker command I used was the default created by CCS. The original array was placed in FRAM.

Then I modified the code so as to place the array and an index variable in .ti.persistent section. No problem there either. (The default linker places the .ti.persistent section in FRAM).

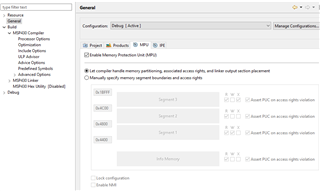

Then I modified the placement of the .ti.persistent section and I moved the array and the index variable (an unsigned integer) to FRAM2. When I did that, first I had an error that was solved changing the memory model to LARGE (and I also changed the option of "what data must be near" to "none") . The program compiled without errors but now, when I checked the area of FRAM2 where the array was supposed to be ... it was empty. No data had been written in FRAM2 and no error messages were reported. Investigating the section that controls MPU, I had kept the default settings created by Code Composer. I decided to disabled the MPU, and the program worked again. I would rather have the MPU active, but it seems that the system doing it automatically creates the wrong settings ... and I'm not sure about how to configure it myself.

Finally, and this is the real reason for my post: I replaced the .ti.persistent in FRAM2 with .ti.noinit . Now the code doesn't work anymore ... I receive some error message with the word "trampoline" and I am not familiar with this concept. I thought the only difference between .persistent and .noinit was related to the initialization. I guess there is more to it? Any help on this will be appreciated.