Other Parts Discussed in Thread: MSP-FET,

If I'm reading the documentation (the Data Sheet and the Family User's Guide) correctly, the four JTAG pins of the MPS430F5359 (TDO, TDI/TCLK, TMS, and TCK) can also be configured as the GPIO pins PJ.0, PJ.1, PJ.2, and PJ.3.

So I wrote some code to try to do that reconfiguration and then wiggle the pins. (You can easily guess what my various macros do.)

// SET_BITS( PJOUT, ( BIT_3 | BIT_2 | BIT_1 | BIT_0 ) );

// SET_BITS( PJDIR, ( BIT_3 | BIT_2 | BIT_1 | BIT_0 ) );

PJOUT = 0xFFFFU;

PJDIR = 0xFFFFU;

for ( uint16 i = 0; i < 10U; i++ )

{

CLR_BIT( PJOUT, BIT_0 );

DELAY_US( 10UL );

CLR_BIT( PJOUT, BIT_1 );

DELAY_US( 10UL );

CLR_BIT( PJOUT, BIT_2 );

DELAY_US( 10UL );

CLR_BIT( PJOUT, BIT_3 );

DELAY_US( 10UL );

PJOUT = 0x0000U;

DELAY_US( 10UL );

SET_BIT( PJOUT, BIT_0 );

DELAY_US( 10UL );

SET_BIT( PJOUT, BIT_1 );

DELAY_US( 10UL );

SET_BIT( PJOUT, BIT_2 );

DELAY_US( 10UL );

SET_BIT( PJOUT, BIT_3 );

DELAY_US( 10UL );

PJOUT = 0xFFFFU;

DELAY_US( 10UL );

}

But when I run this code, only TDO (PJ.0) wiggles.

The documentation states that the TEST/SBWTCK signal has some control over this but when that pin is pulled down to VSS, GPIO ought to be available; I have external logic on my board that IS pulling that pin down.

The documentation also discusses the SYSJTAGPIN bit in the SYSCTL register but the point of this is to disable GPIO use so I'm leaving that register in its default BOR state (and setting that bit DOES seem to disable my successful use of PJ.0).

Note:

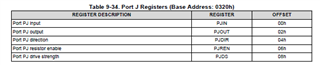

Port J doesn't have a "SEL" register to select whether the pins are GPIOs or Peripheral Function pins.

Does anyone know why I can only get PJ.0 to work as a GPIO and not PJ.1, PJ.2, or PJ.3?