Tool/software:

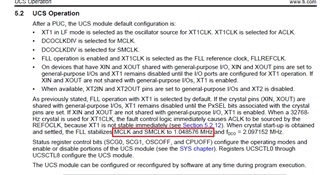

as the default start-up MCLK and SMCLK to 1.048576 MHz

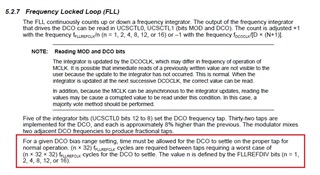

so, in first start up the MCLK and SMCLK should not settle to 1.048576 MHz (need wait settle time).

Is there any error specification of SMCLK during this time (e.g. - 20%)?

Because this SMCLK also use for watchdog at first start up (may not 31.2 ms as the clock deviation)