Tool/software:

Hi,

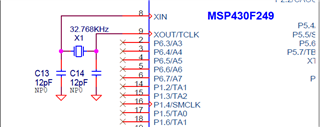

I am using the example code to enable UART msp430x24x_uscia1_uart_05_9600.c for MSP430F249

The example codes works fine when I run the code through IAR.

I can see the output with the character I enter in the Teraterm port (9600 baudrate).

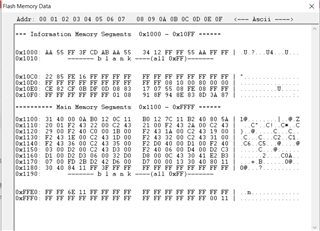

When I use the HEX Image and flash using FETPro Tool, Its not working. I mean the RX input is echoed to TX.

Please help to identify the issue.