Hello everybody!

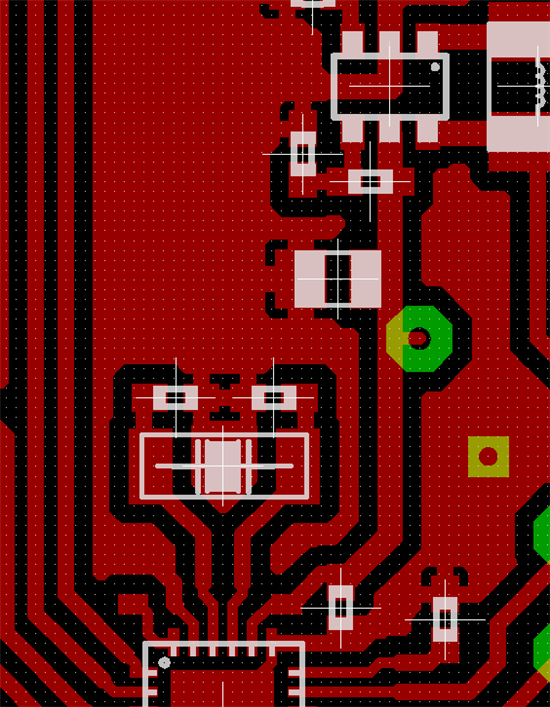

I have a problem with starting XT1 crystal oscillator in 32768 KHz mode on MSP430FR5720. It just does not start. The scope attached to the ACLK monitoring pin shows the VLFO frequency (about 8 KHz). The crystal is designed for 7.5 pF load, I use 9 pF external caps on both XT1 pins. Tried several cryslats with various load caps in the range 6pf - 12.5 pF and increased external caps up to 20 pF. Development is done in IAR Workbench, the programmer is MSP-FET430UIF, debugging protocol is Spy-Bi-Wire. The circuit is powered directly from the programmer at 3V.

I tried the code below on FR5730 and FR5728 with no luck. The last two lines in this snipplet are modified from the example code msp430fr57xx_LPM3_01.s43 and others from the same examples set where XF1 is used. The original lines in these examples

cmp.w #0x01,&OFIFG ; Test oscillator fault flag

jz OSCFlag

do not make sense for me since OFFIFG is not a valid SFR name. I tried these lines anyway, but it does not work too. The debugger shows both flags XT1OFFG and OFIFG are set no matter how long I cycle in the oscillator starting loop. Here is my code.

reset: mov .w #SFE(CSTACK), SP ; set up stack

mov.w #WDTPW+WDTHOLD, &WDTCTL ; stop watchdog timer

mov.w #0x0F, &PJDIR

bis.w #BIT5+BIT4, &PJSEL0 ; enable Xtal oscillator pins

bis.w #BIT2, &PJSEL0 ; enable ACLK monitoring pin

mov.b #0xA5, &CSCTL0_H ; unlock the clock interface

mov.b #XT1DRIVE_3, &CSCTL4_L ; crystal drive level (tried _0 - _3)

wco1: bic.w #XT1OFFG, &CSCTL5 ; clear XT1 fault flag

bic.w #OFIFG, &SFRIFG1

bit.w #OFIFG, &SFRIFG1 ; test oscillator fault flag

jnz wco1 ; wait for crystal osc. to start

I would appreciate any advise for a direction to follow. The problem drives me crazy, as everything else works fine with VLFO if I disable the last jnz instruction.