Tool/software: Code Composer Studio

hi all:

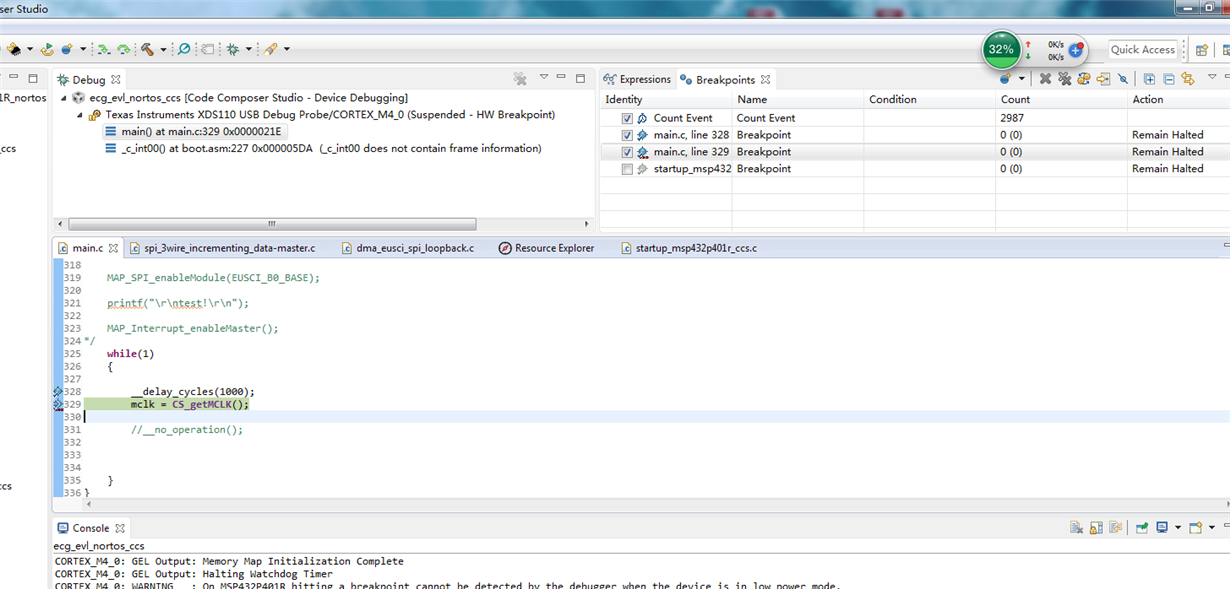

I need me to get the exact time of the program.So the method of using COUNT clock cycle in CCS DEBUG . I use the __delay_cycles () precise delay program for 1000 clock cycles.

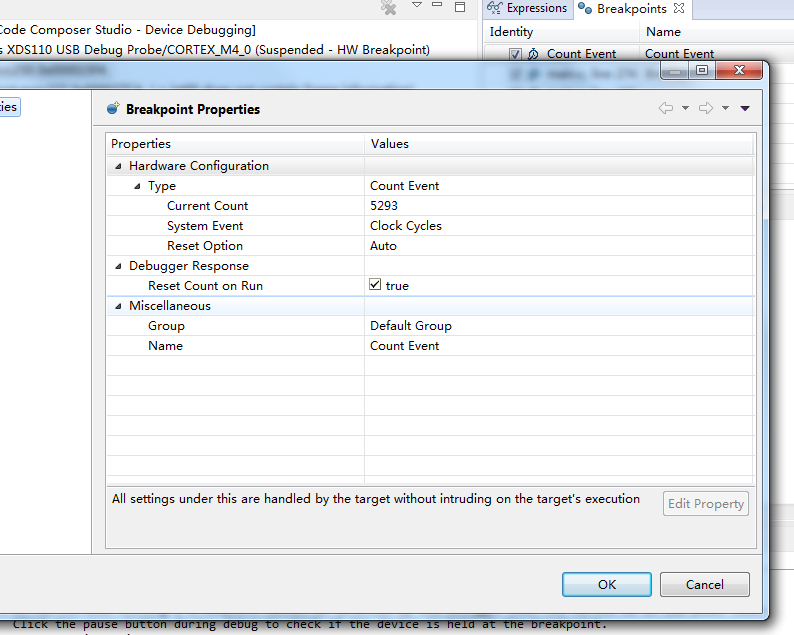

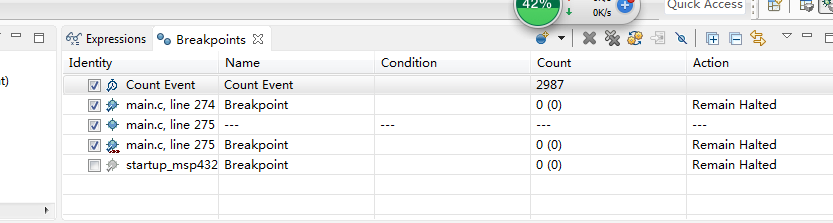

Then read the value of count to see if it matches.The breakpoint of the program and the settings of the CCS debug breakpoint count are shown in the following picture.

After the program is run, the clock cycle is not 1000, but 2987, between the two measuring breakpoints of the program.As shown in the following picture

This is my doubt, I accurately delay 1000 clock cycles, why the CCS breakpoint count calculates the clock cycle is 2987?