QUESTION:

- Does the MSP430FR2676 have the Enhanced Clock System or Not?

- Can I have VLO be the source for ACLK?

Thank you so very much :)

Willie

-------------------------------------------

VERY Difficult to Tell from Datasheet or User Guide: (my guess is YES - Enhanced CS)

- Page 55 of Datasheet (SLASE05C) - States:

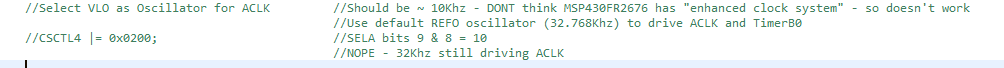

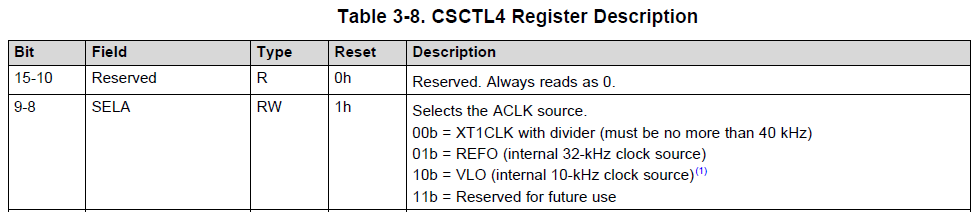

"Auxiliary Clock (ACLK): This clock is derived from the external XT1 clock, internal VLO or internal

REFO clock up to 40 kHz".So would think maybe this is a newer part and has the enhanced Clock System - but only goes to 16Mhz not 24Mhz (enchanced CS) - so again confusing.

- Page 98 of User Guide (SLAU445I) - Table 3-1 does not list MSP430FR2676:

- So not sure if enhanced or not

- I know there was a post related to this when I searched - but for a different part #.about 1 year ago - so thought would ask again if ok.