Other Parts Discussed in Thread: DRV8838

Hi,

We are trying to establish SPI between MSP430G2131(slave) and CH341A(master) to control the potentiometer. The goal is to read the potentiometer data from the DRV8838 EVM board and transfer it from the slave to the master.

To verify that the MSP430G2131 chip works correctly as a slave, I am currently establishing a SPI communication between 2 MSP430G2131 chips.

I have a few questions as below:

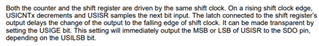

- Page 403 of the msp430x_2xx user guide (pdf) mentions

- Is there any difference between the shift clock and the SMCLK?

- Why are we given an option to configure USICKPH and USICKPL if it is fixed that USICNTx decrements and USISR samples the next bit input on the rising clock edge?

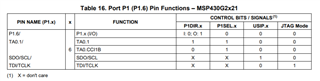

- I am a little confused about the difference between PxIN, PxOUT, PxDIR and PxSEL registers.

For instance, in the example codes:

SPI Slave config

- How can we configure ‘P1.1 as output rest input’ in P1DIR and then set P1.4 in P1OUT? Does that mean both of the pins are acting as inputs?

SPI Master config

- How is P1DIR used to reset the slave?

DRV8838_CstomerEVM_Default _Code

- What is the function of the above statements?

- What is the difference between P1SEL and P1DIR and P1OUT?

- I am trying to send hardcoded values from the master to the slave and vice-versa. I can see the waveform on P1.6 pin (of MSP430G2131) after I hardcode a value of the USISRL register but not if I hardcode it into the P1OUT register. Doesn’t USISRL register transfer the data to the P1OUT register before transferring?