Other Parts Discussed in Thread: DRV8350

Hi,

During the verification of our last design based on DRV8350S-RTV, we have observed that a combination of >44 V DC bus and a positive phase current (current leaving the drive towards the motor) causes a glitch in the phase voltage that seems to come from a drop in the High-Side gate voltage right after its rising edge.

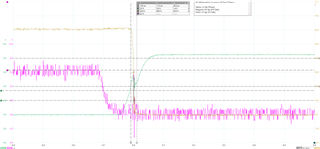

When the current increases, the glitch gets as big as this

If an even greater current is demanded, commutation stops, and the gate driver reports a GDUV fault.

Then, apart from its clear relation to greater voltage and current, we have observed the following:

- The higher the PWM frequency, the deeper the glitch is. The product uses 4 PWM frequency presets: 20 kHz, 50 kHz, 100 kHz, and 200 kHz.

- Happens in 6x PWM mode and gets worse in Independent PWM mode (we use the second).

- With a longer deadtime it gets slightly worse. When there exists a small beginning of a shot-through the glitch almost disappears (obviously not a solution).

- Lowering the IDRIVEP_HS down to 300 mA seems to be the only effective solution, but the slow charge is limiting the small our minimum ON time can be.

Our hypothesis is the charge pump is not able to sustain a sufficient voltage during the charge of the high-side, but we don't have a clear explanation why. Although the VCP capacitor is 1 µF, 25 V, X7R, and the charge-pump switching node capacitor is a 47 nF, 100 V, X7R, following the datasheet recommendations, and the VM is supplied with 9.4 V, the high-side voltage decreases with the DC bus voltage and the magnitude of the positive current, reaching levels as low as 4.5 V and even less.

We would deeply appreciate any help on this topic, willing to complement this info with any other data you may require.

Thanks.