Other Parts Discussed in Thread: BOOSTXL-DRV8301, LAUNCHXL-F28027F, DRV8301,

Hi There,

I have been trying out the boostxl-drv8301 paired with the launchxl-f28027f to do FOC control with a brushless motor. It has been working great! I've been using example project 5h.

However, I've designed my own board with not quite the same chips, and having some issues. I think it's probably something simple missing with the gate driver.

- Instead of f28027f MCU I am using f28026f which also has InstaSPIN enabled.

- Instead of DRV8301, I am using DRV8300, becuase the 8301 and other gate drivers are out of stock. (by the way, any idea when the 8301 will become available again?).

I've actually replaced the f28027f with a f28026f chip on the launchxl-f28027f eval board, and if works fine after changing the linker file.

On my board, I've added some external feedback circuitry that the 8300 does not provide. Other than that, the connections are pretty much identical to the two eval boards.

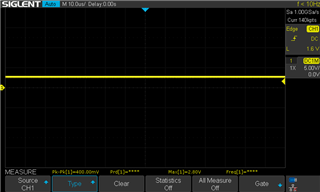

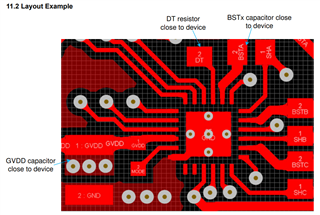

The problem I am having is that the gate driver isn't outputting anything. The bootstrap pins are at my supply voltage (16V), and I have tried a range of bootstrap capacitor values between 0.047uF to 10uF. But still, I seem to measure a voltage drop across the capacitors which would put the 8300 into UV lockout. BUT, maybe I'm measuring this wrong (without any outputs at expected frequency). Like I said, I've tried many cap values with no luck.

I have modified the user.h parameters to reflect my feedback circuit, and have verified that they work OK.

Other potential issue:

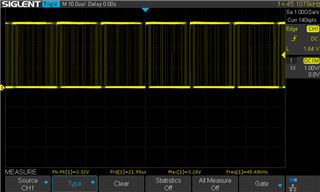

When I compare the PWM output signals on my board, to the eval board, there is a lot of transient noise in my signals... I can post a scope shot later. I'm wondering if this is preventing the 8300 from outputting anything, or if it's a result of no output at all.

When I run the program in debug mode and turn on the outputs, it goes into a run active mode like I would expect, but nothing happens on the gate driver side.

Any guidance would be much appreciated. Thanks!

Alec