Recently, we designed a motor driver. After power on, we found that the nFAULT pin reported an error. After reading the SPI controller, we found the GVDD_UV, then measure GVDD pin, found to be zero volt, excuse me, why this problem?

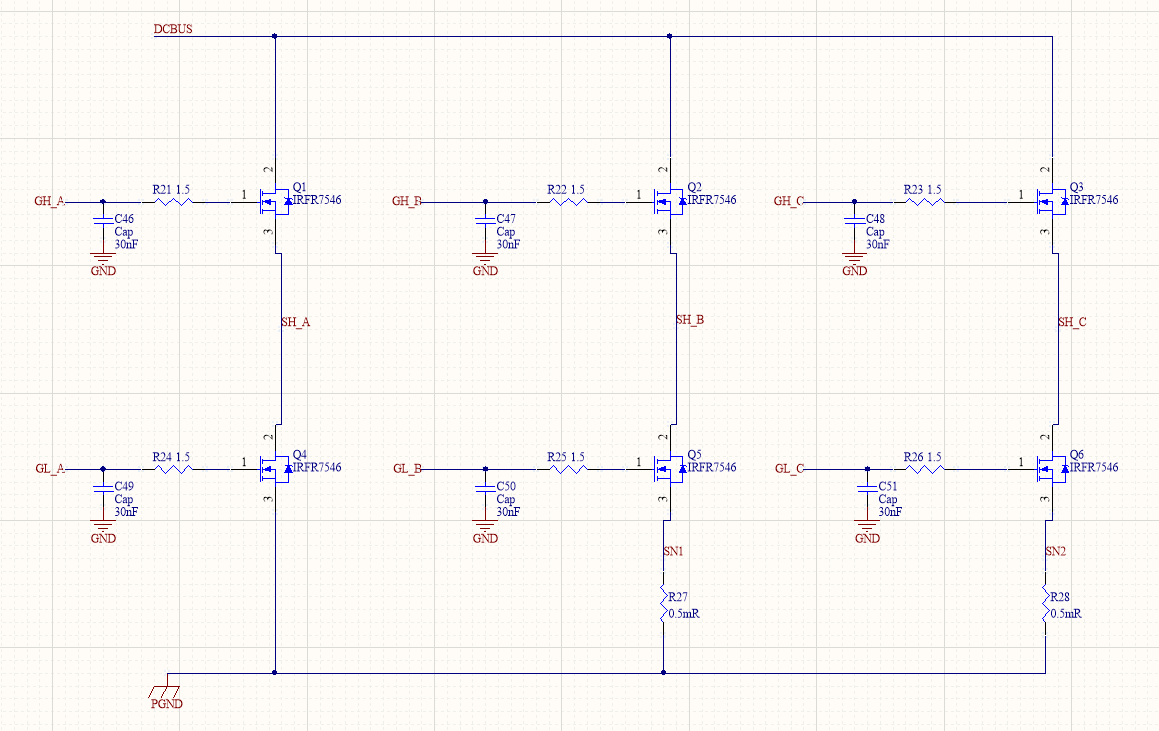

Here is our schematic:

The gate capacitor in the schematic is not welded