Hi team,

Here's an issue from the customer may need your help:

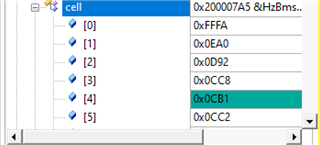

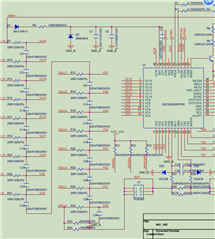

Design the board based on the chip manual and evaluation board related circuitry. Regarding the control of the FET, CHG and DSG cannot be controlled individually, issuing one of the instructions to the chip: DSG_PDSG_OFF, CHG_PCHG _OFF. The MOS tube cannot be controlled independently, the state is always jumping, and when the FET state is read, the state is always jumping and cannot be stable.

Could you help check this case? Thanks.

Best Regards,

Cherry