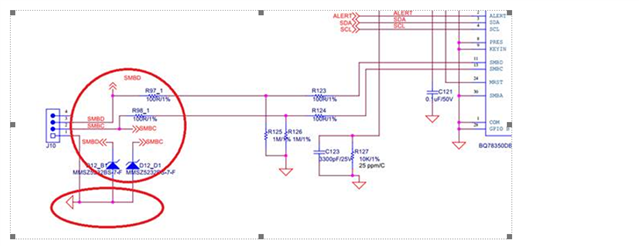

Other Parts Discussed in Thread: BQ76920, , TIDA-00792, , BQ769200, TIDA-01093

Dear ,

Could you please help to check the circuits of several TI chips?

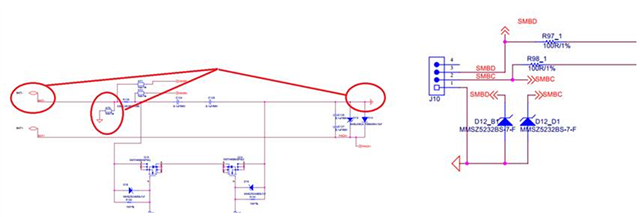

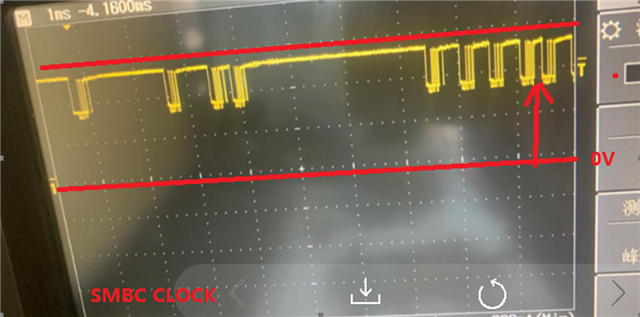

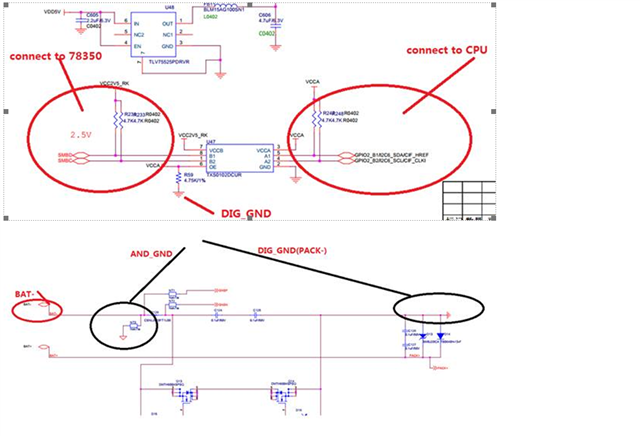

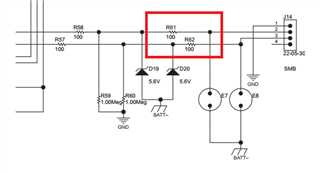

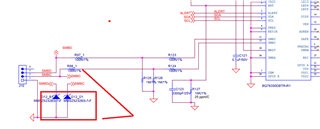

Especially for BQ79620 and BD78350, I measured that there is a 0.4V difference between analog ground and digital ground directly, and the following two diodes are easy to be damaged and burned, so I want to confirm whether the relevant circuit is correct?the schematic is attached as below ,many thanks