- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello TI Team,

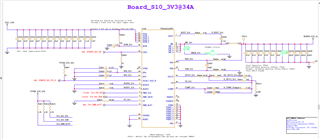

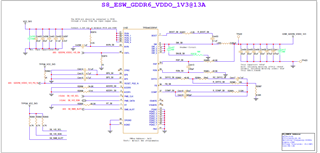

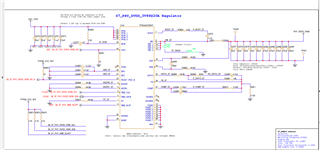

We have done the schematic design of TPS546C23 buck- regulator with help Design Excel sheet calculator. Kindly review the Schematics, Bode Plot and thermal point view and share your valuable feedback.

Requirements:-

Design 1. 1.3V@10-13A , O/P ripple= 10mVp-p, Voltage tolerance= 1%, Vin=12Vdc, FSW=300KHz

Design 2. 3.3V@30-34A, O/P ripple= 9mVp-p, Voltage tolerance= 5%, Vin=12Vdc, FSW=300KHz

Design 3. 0.88V@16-20A, O/P ripple= 20mVp-p, Voltage tolerance= 3%, Vin=12Vdc, FSW=300KHz

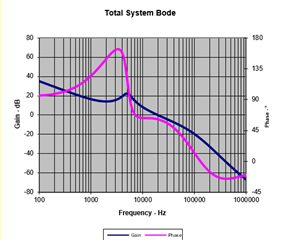

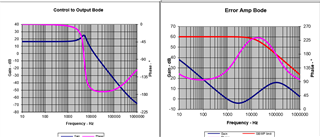

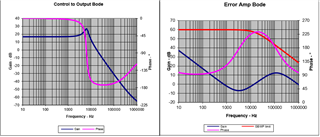

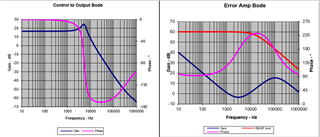

We have attached bode plot from design calculator Please review Bode Plot (for Compensation circuit confirmation)

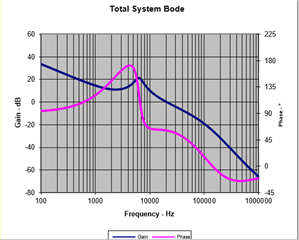

Design 2:- 3.3V@30-34A, O/P ripple= 9mVp-p, Voltage tolerance= 5%, Vin=12Vdc, FSW=300KHz

Phase Margin=61.4Deg.@20.2KHz cross over frequency

Gain Margin=-23dB

IC Power Dissipation:- 4.069W(As per calculation TJ going Out of recommendation)

-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

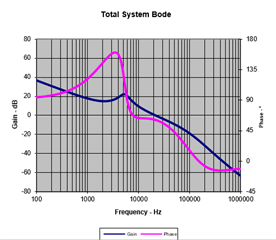

Design 1:- 1.3V@10-13A , O/P ripple= 10mVp-p, Voltage tolerance= 1%, Vin=12Vdc, FSW=300KHz

Phase Margin=61Deg.@20.5KHz cross over frequency

Gain Margin=-25.3dB

IC Power Dissipation:- 3.265W(As per calculation TJ going Out of recommendation)

---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

Design 3:- 0.88V@16-20A, O/P ripple= 20mVp-p, Voltage tolerance= 3%, Vin=12Vdc, FSW=300KHz

Phase Margin=60.5Deg.@22KHz cross over frequency

Gain Margin=-25.9dB

IC Power Dissipation:- 2.7W(As per calculation TJ going Out of recommendation)

Please help here in reviewing and share your comments.

Thanks & Regards,

Prasad Tatar

Hi Prasad,

I finished reviewing, and I think the schematics look good.

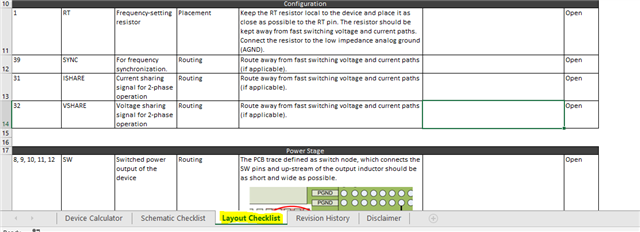

When you start the PCB layout, please follow our layout guidelines for AGND and PGND connections, as it was not clear from the schematic symbols. For example, BP6 needs to be bypassed to AGND and other signal components such as RT, etc.

You can use our Excel checklist for the layout as well:

Thank you for the reply Tomoya.

1) How about Design 2 because Device supports 35A and Our Requirement worst scenario is 32A with 9mVpp ripple requirement will be suitable?

2) All 3 design, Thermal Point of TJ going beyond recommended TJ, Kindly suggest here.

3)all Bode Plot are fine ?

Please help here to get this confirmation so we will conclude this design.

Thanks & Regards,

Prasad Tatar

1) How about Design 2 because Device supports 35A and Our Requirement worst scenario is 32A with 9mVpp ripple requirement will be suitable?

9mV ripple should be achievable with Design 2.

2) All 3 design, Thermal Point of TJ going beyond recommended TJ, Kindly suggest here.

Could you tell me how you got to that conclusion? Our design tool does not provide thermal information. For example, how did you get the IC power dissipation calculation?

3)all Bode Plot are fine ?

Yes, all Bode plots shown look good.

Hi Tomoya,

Thanks for the review.

As per your feedback, I will Proceed with this design.

We referring IC power dissipation from web bench simulation and that we are applying into standard TJ formula.

Thanks & Regards,

Prasad Tatar