Hi,

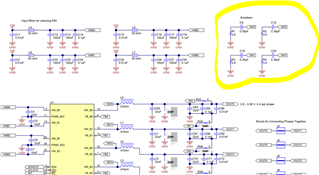

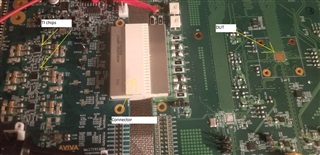

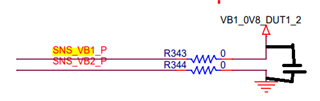

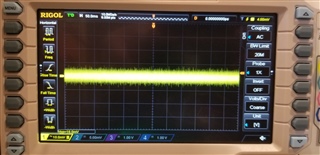

schematics is attached. the design is done, and the board is in the lab. The voltage come out properly and the current and voltages can be read. however, i am not trusting the current reading. the main issue is that the chip gets hot under no load condition. Does not matter if you have any load on the power supply, the chip gets so hot that you cannot touch it. under no load, I am noticing that the chip draws about 1.5A. Please review the design and let me know how to resolve the issue...

thanks,TI_Review_09232022.pdf

Habib