Other Parts Discussed in Thread: BQ25306, TPS25947, TPS25947EVM, LM5118

Hi,

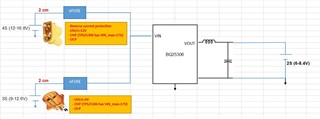

I want to use the TPS25942A eFuse IC to connect two external power sources/batteries 4S (12-16.8V) and 3S (9-12.6V) to the Li-Ion 2S battery charger BQ25306.

The external power source/batteries are connected only separately and mechanically protected to connect them simultaneously.

The connector pins of 4S (12-16.8V) are accessible to make a single point of failure when the 3S (9-12.6V) battery is connected.

When the 4S (12-16.8V) battery is connected the second battery 3S pins are covered and not accessible from a single point of failure.

System requirements:

Vin1= 4S (12-16.8V)

Vin2= 3S (9-12.6V)

Iin_max=2A

Have to support:

a. UVLO_1=12V and UVLO_2=9V

b. Reverse current protection

c. OVP (TPS25306 has maximum operational Vin=17V)

d. OCP - is optional. It's supported by the Li-Ion 2S battery charger TPS25306

1. What is the TI IC's best option to support my requirements?

2. Could you please clarify why all eFUSE ICs have huge tantalum capacitors at the output 100uF?

3. Can I eliminate or use a small ceramic capacitor instead for my configuration that does not require energy storage? Is the BQ25306 Cin=2.2uF enough to serve the both BQ input and eFUSE output?

4. What do you think, is my system assailable to the input hotplugging? or the charger (Li-Ion 2S battery charger BQ25306) turn-on activation time will delay the high charging current appearance and will nature eliminate the hotpluging phenomena? The input battery is connected with very short (~2cm) and thick wires.

Thanks

Vitaliy