This may be related to a previously reported issue though has been seen to occur at low and ambient temperatures: https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1235920/tps25982-cannot-turn-off-at-low-temperatures--30c

I'm experiencing an issue with the TPS25982 smart efuse where it occasionally does not turn OFF despite EN being pulled low. Output will remain at 12V and source current until the input power supply is cycled at which point it will then behave as expected until the issue recurs.

The latch-up failure has been observed at various package temperatures from -40°C up to 15°C. Most of our observed failures happen at low temperatures <-20°C. We have observed rare failures up to 15°C. Failures at low temperatures seem to recur more reliably than those at ambient temperatures (ie. ICs that show latch-up at low temperature tend to have every enable-disable cycle at low temp remain latched up, very rare to observe latch up at ambient temperatures).

The failure has been observed with and without loads connected (ie. output is disconnected, only measuring output voltage via voltage divider).

The failure has been observed with and without schottky diodes installed on output to clamp any negative voltage transients.

We have several dozen other TPS25982 ICs in an identical, unmodified circuit that have never exhibited this behavior. Replacing the faulty ICs tends to resolve the issue but we can't reliably induce the failure to confirm this.

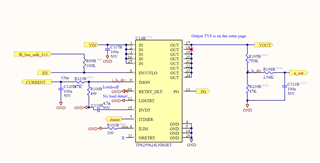

Schematic is shown below:

VIN and VOUT both have TVS diodes to GND.

Plot showing latching behavior:

V_IN remains at approx 13V.

EN cycles on and off. I've confirmed with scope that the EN pin voltage matches the shown boolean behavior (1 = high = 3.3V measured, 0 = low = 0V measured)

V_OUT behaves as expected for 1 cycle. On the second cycle, V_OUT remains high despite EN going low.

Do you know what might be causing this? How can we mitigate this failure?