- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hello!

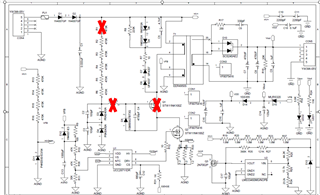

I am currently experimenting with an SMPS based on the "400- to 690-V AC Input 50-W Flyback Isolated Power Supply Reference Design for Motor Drives."

Contrary to the guide, I am not using a cascade connection at the moment. I am using a single MOSFET as shown in the diagram, and the MOSFET is the same as the one selected in the guide.

Currently, only the initial 3 PWM pulses are being output, and the system is not operating properly. Therefore, I measured the VS and CS pins.

To minimize risks during measurements, I kept the lead wires short. My experimental setup is as follows:Red circle are lead cable using measurement.

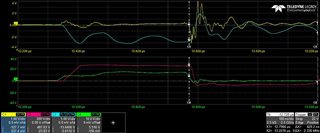

For the CS pin voltage: It is in a no-load condition with a shunt resistor of 1.2 ohms. I observed the following waveform. I think this voltage spike is caused by the measurement cable. Therefore, I believe it has not reached the protection voltage. Could you provide any comments on this?

(CH1: Vcs, CH2: VDS, CH3: Vaux, CH4:Vgs//Test input voltage : 500Vdc)

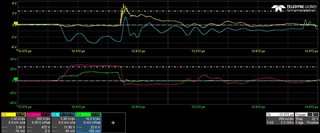

(CH1: Vcs, CH2: VDS, CH3: Vaux, CH4:Vgs//Test input voltage : 500Vdc)For the VS pin voltage: It is also in a no-load condition, and the waveform is as follows. I think the current voltage on the VS pin is higher than the operating level. So, I am considering reducing the value of R_vs. Could you provide any opinions on this?

(CH1: Vvs, CH2: VDS, CH3: Vaux, CH4:Vgs//Test input voltage : 500Vdc)

(CH1: Vvs, CH2: VDS, CH3: Vaux, CH4:Vgs//Test input voltage : 500Vdc)

Hi Seungypo,

Thank you for reaching out.

1. The CS pin does seem to have a lot of oscillations. This could be due to probe inductance. From the timescale of 100ns/div, this spike on CS is within the leading edge blanking duration and it should not cause tripping. But I would recommend using a spring tip probe to obtain the best results.

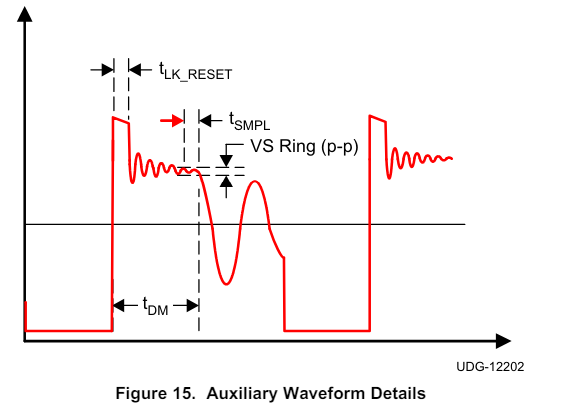

2. The Vs pin is not recommended to be probed, but as long as it is a long low pf cap probe it could be ok. The Vs pin does not look ok as it does not reach regulation level also. It could be to OVP. I think the AUX winding needs to be cleaned to get a good sample as detailed in the datasheet shown below.

3. There is a internal negative clamp of -250mv to which Vs is clamped during MOSFET on time. Please check the electrical characteristics section of the datasheet. Only the AUX winding voltage will be input voltage (negative) divied by the turns ratio Npa.

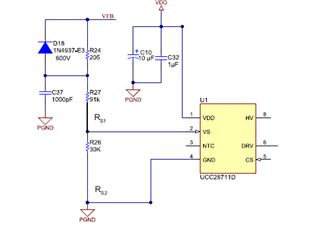

The diode is added probably to balance the effect of noise coupling to the Vs pin. Also there is a zener + diode which is recommended to ensure the current into the Vs pin is protected/ limited to 1.2mA. Please refer the following link:

Regards,

Harish