Is power up sequence timing depend on external charge pump circuit?

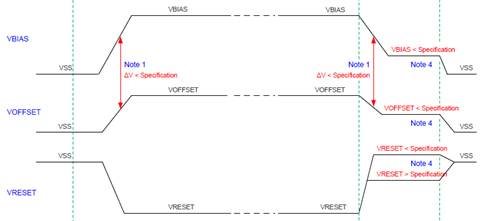

For example, below application note P2, use case of lower Negative Charge Pump.

※Boosting Positive Charge Pump is not use.

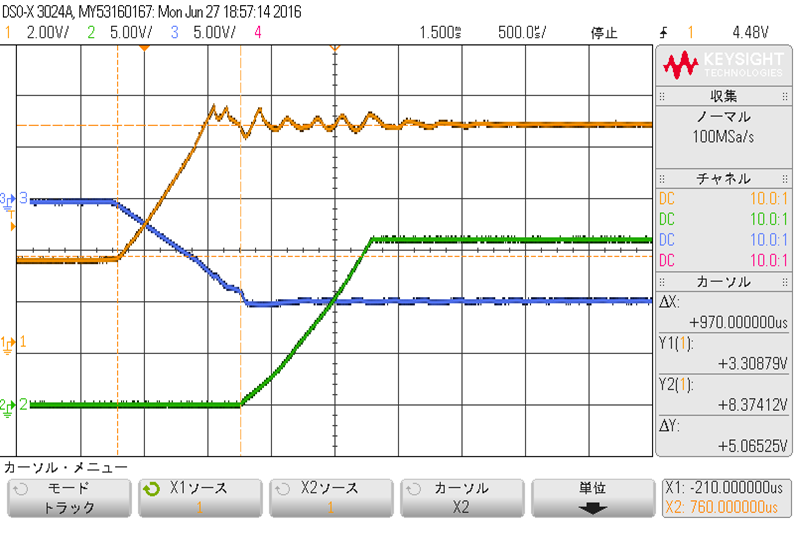

These sequence timing is attached, ch1 and ch3 ware the same timing.

※1ch:8.5V, 2ch:16V, 3ch:-10V

Best regards,

Satoshi