Other Parts Discussed in Thread: UCD74120, , UCD9244

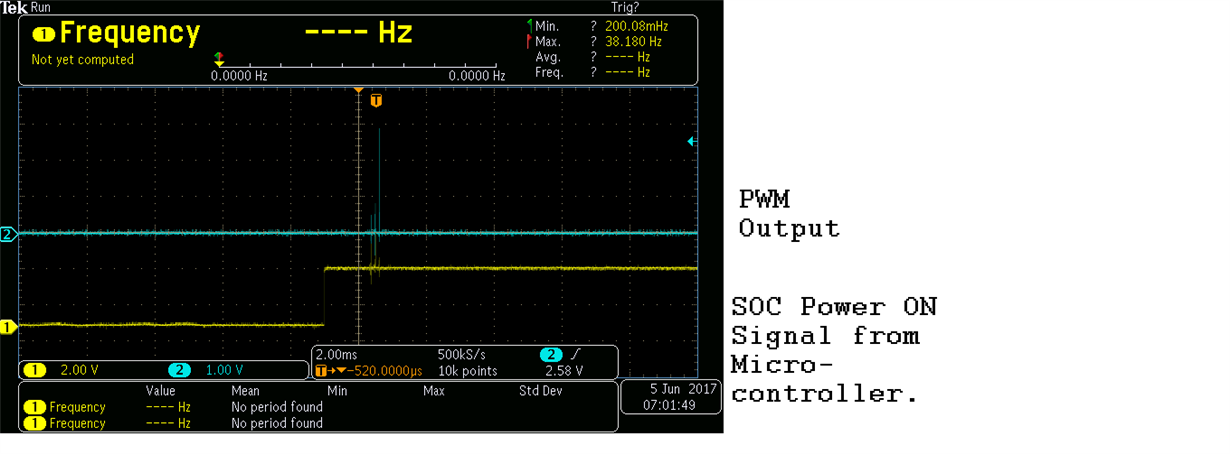

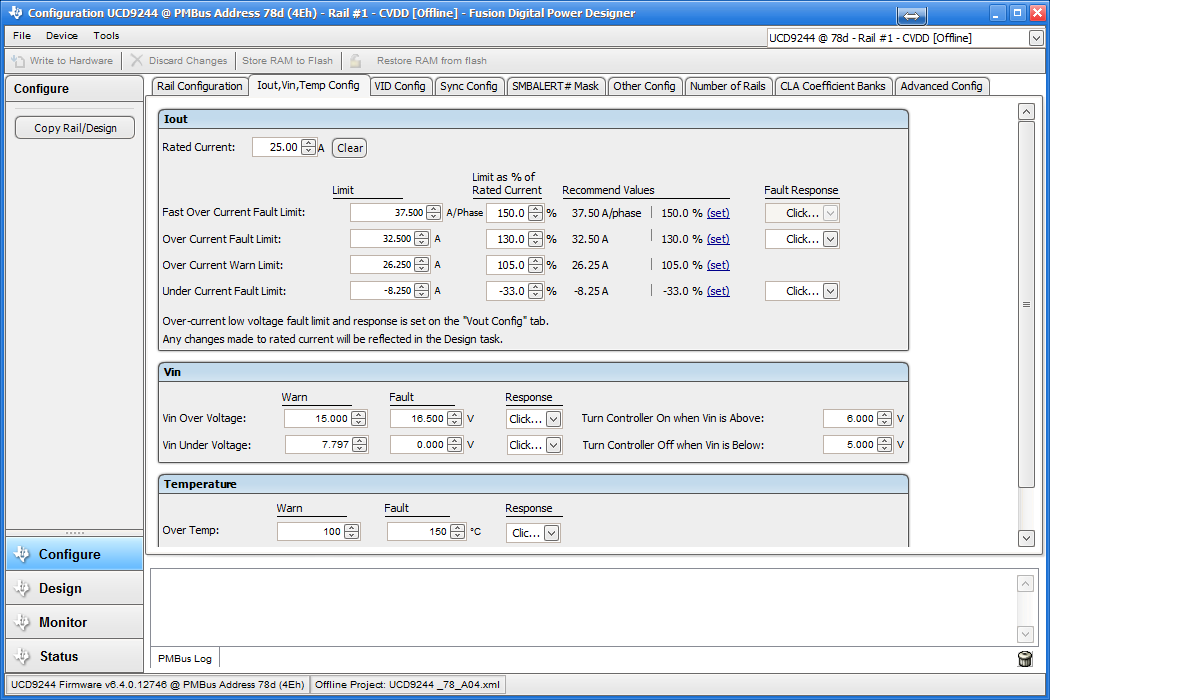

We have assembled our board and facing issues in powering up the SOC (K2K). We are consistently seeing SOC power failure in the LCD of Microcontroller.We have made sure all the UCD files being used are the latest. We picked it from the Advantech web-site.

The UCD configurations were picked up from the below link.

http://www2.advantech.com/Support/TI-Evm/EVMK2HX_sd4.aspx

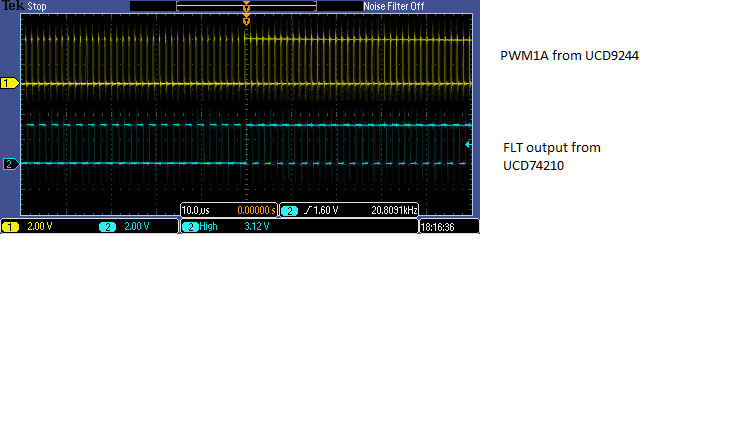

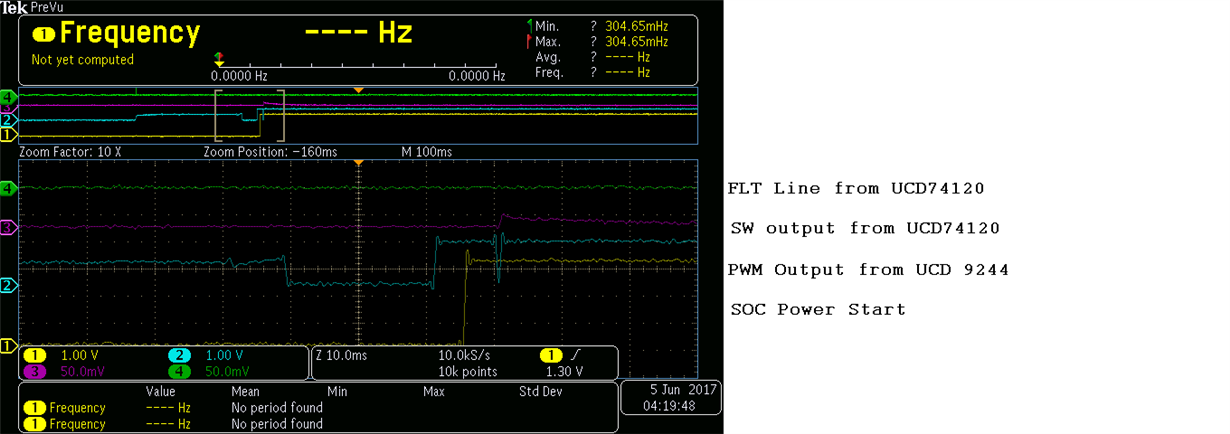

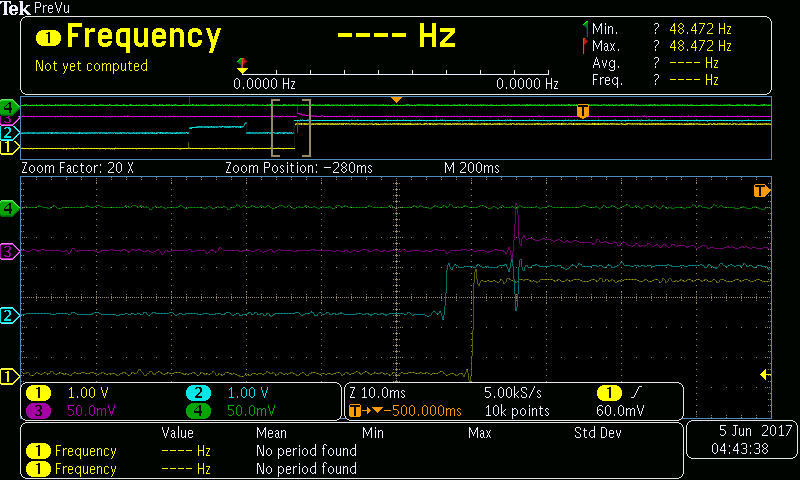

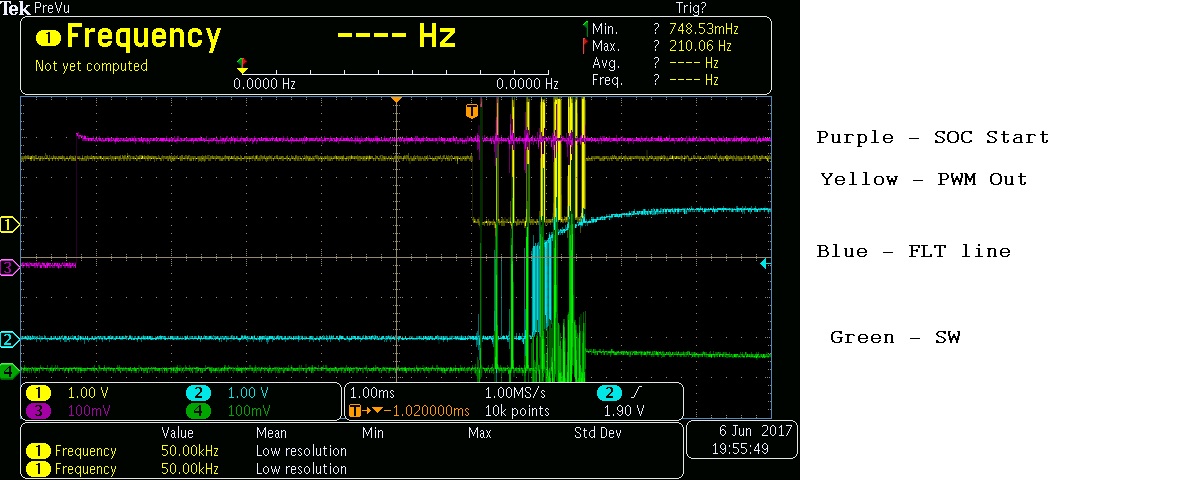

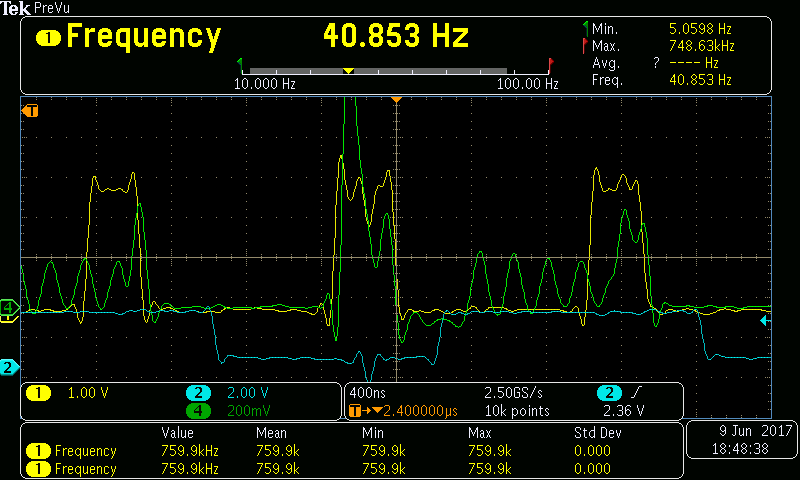

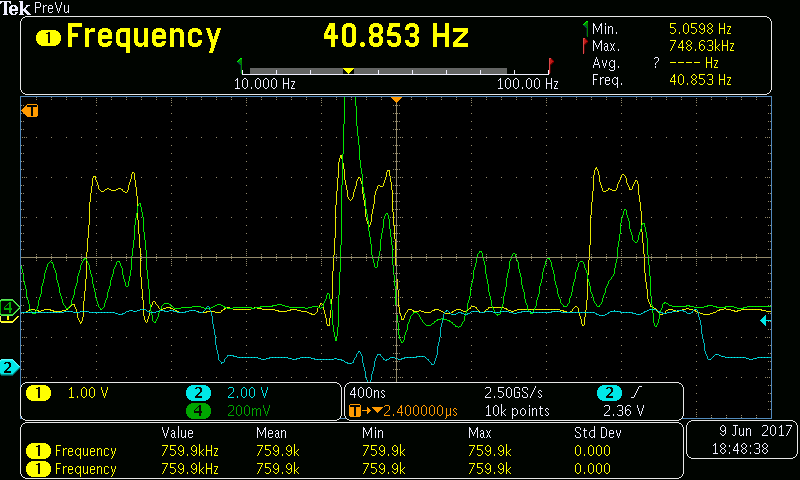

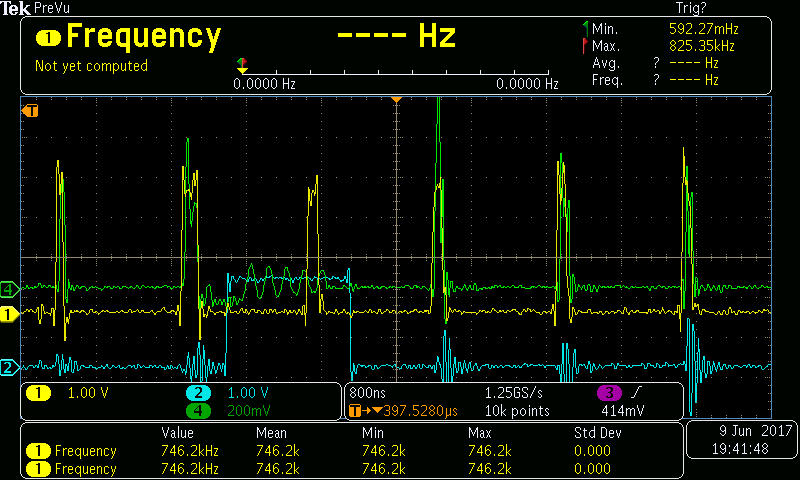

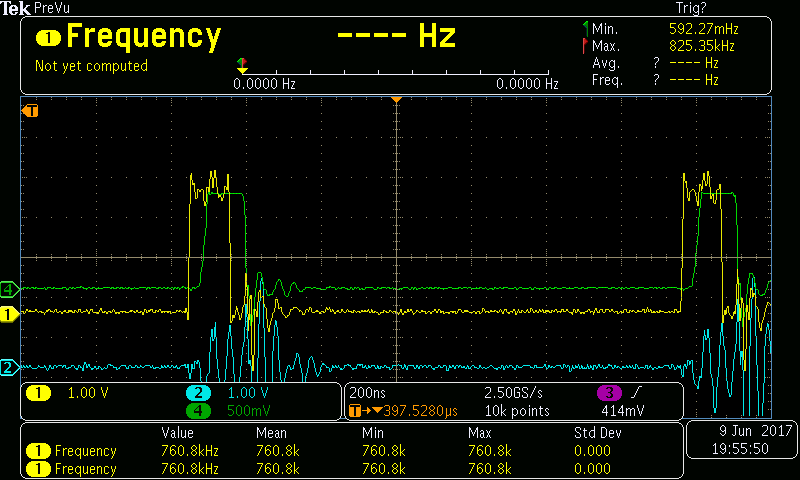

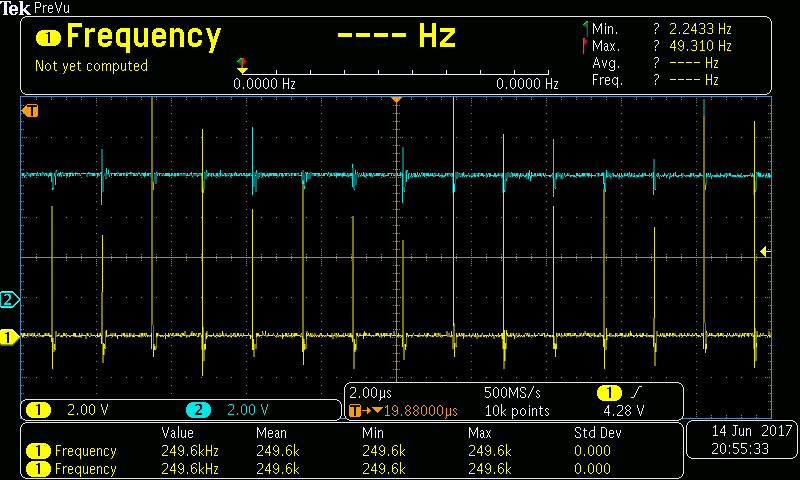

On the UCD9224 we are seeing both of the rails reporting a FLT line from both the UCD74120. PFA the schematics and the oscilloscope plot depicting the FLT line behavior with PWM output.

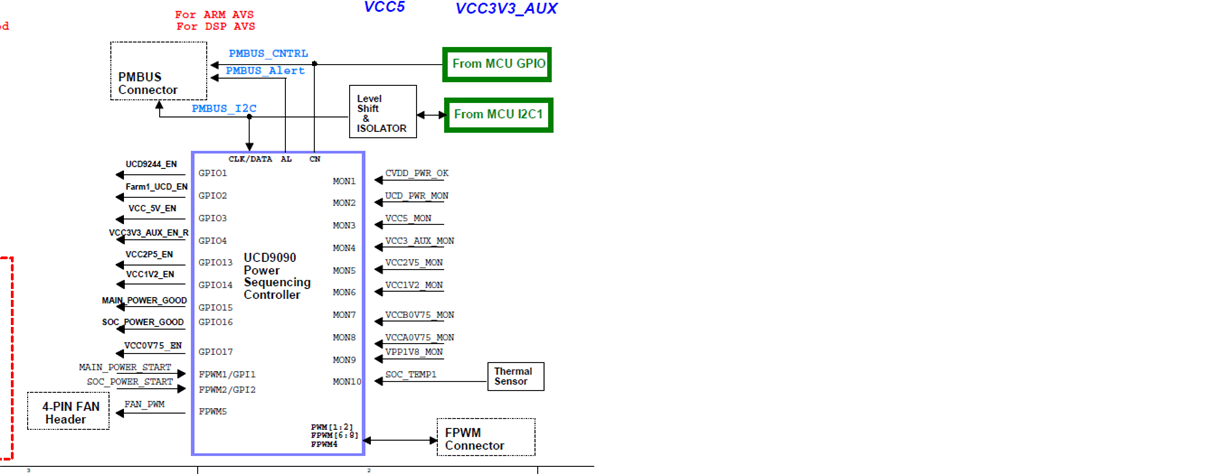

Below is the scheme of power design used. We have been re-using the design from K2K EVM from Advantech.

We are observing that the FLT line is oscillating during the PWM cycles. Attached is the oscilloscope capture ,the schematics of the same and the Fusion software captures6574.UCD9244 6.4.0.12746 Address 78.docxK2K-CVDD-PWR-Section-Sch.pdf