Other Parts Discussed in Thread: TMDS64EVM, AM6442, LMK1C1104, AM3352, AM62A3-Q1, AM62L, OMAP-L138, AM62A7

Hi TI Experts,

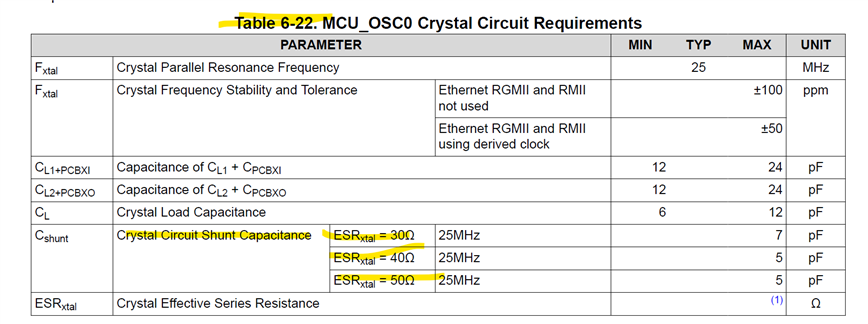

I have the below queries regarding the crystal selection.

- Recommended crystal frequency for MCU_OSC0

- Do you have recommended part numbers for Crystal?

- Can you help check if NX2016SA-25MHZ-EXS00A-CS10694, CRYSTAL 25.0000MHZ 8PF SMD could be used?

- Do you have recommendations for MCU_OSC0 crystal selection.

- Could you share the crystal part number used on the EVM?

- Can i use an oscillator as the clock source?

- Is there a real max value for crystal ESR?

- Is there some guidelines for the crystal circuit layout?

- Is there a delay requirement for the MCU_PORz after all the power supplies ramp and does the delay depend on the clock source

Let me know your thoughts.