Hi all,

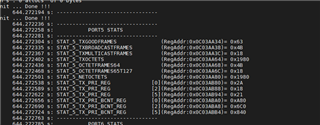

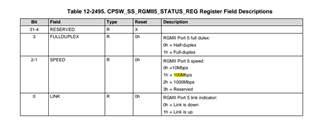

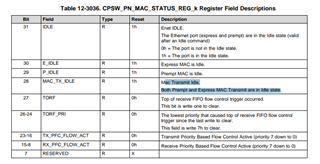

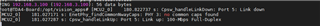

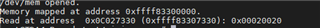

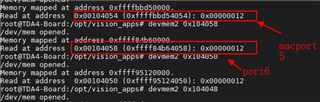

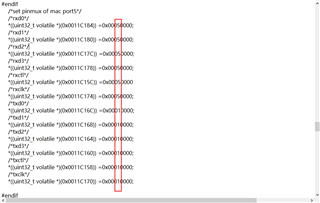

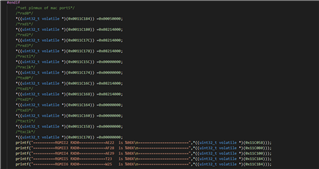

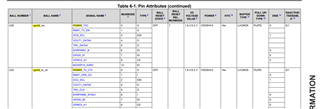

When we use psdk 7.2 in our customed board, Ethernet can be applied properly except for the macport which is connected with rgmii5. As the result of Rgmii5_tx_clk is in 2.5MHz, the phy can be linked up but no data packages can be send to the cooresponding macport. we have checked that there is no difference between other available 100M rgmii and rgmii5. Also we read-back checked the pinmux registers, the result is same as the configuration we have make as below.

So, could you please help me to solve the problem, and i wonder if there is conflict configuration for the pin below in psdk.

thanks