Building the udma_baremetal_memcpy_testapp from the RTOS SDK, I've tried to load it onto the MCU2_0 core by performing the following (boot via SD-card):

Hit any key to stop autoboot: 0

=> rproc init

=> fatload mmc 1 0x80000000 /anton/memcpy_test_for_t3_mcu2_0_release.xer5f

2540972 bytes read in 66 ms (36.7 MiB/s)

=> rproc load 4 0x80000000 2540972

Load Remote Processor 4 with data@addr=0x80000000 39061874 bytes: Success!

=> rproc start 4

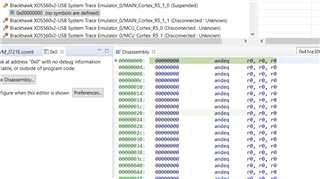

I then open CCS to verify that the application is running, but I only see that the ATCM area (0x00000000--0x00007FFF) is empty:

To my understanding, when loading from u-boot, the ATCM is enabled per default and that the application needs to have its reset vectors in ATCM.

I see that the .map file for the binary I've built does not use this area.

Is there an example of how to set up the linker file, to add the reset vectors into ATCM area?

Here is how I built the binary from the PDK/build folder:

make udma_baremetal_memcpy_testapp CORE=mcu2_0 -sj