Dear Experts,

The custom board design housed with an AM3359 processor connected with an FPGA over GPMC interface, which is operating at 100MHz, Synchronous & Multiplexed mode.

The AM3359 processor is running with Linux SDK v6.1.

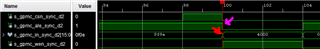

There is an issue with address placement on the bus and ALE alignment is inconsistent. Attached the snapshots for understanding and highlighted with clock mismatch output.

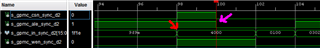

The alignment of ALE and ADDR is proper in some transactions, image as follows,

Please share your inputs and possible reasons behind this.

Thanks