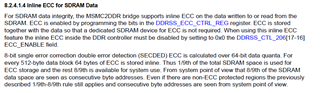

Enabling inline ECC for memory size <= 2GB is simpler as the memory address range is with in 32 bit address(0x80000000. - 0xFFFFFFFF)

How to enable Inline ECC > 2GB address.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.