Hi all,

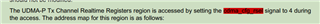

I'm reading the chip manual for TDA4VM (SPRUIL1B.pdf) and have some doubts about the content of the description of the UDMAP register:

Taking the UDMASS_UDMAP0_CFG_TCHANRT register as an example, the description in the manual is as follows:

But in the chip manual I didn't find a description about the cdma_cfg_resl signal.

I noticed the description was due to my attempt to read the register, which resulted in a kernel panic.

My question is what should I do ahead of time in the code if I want to access this register?

Looking forward to your reply。

Best Regards