Hi team,

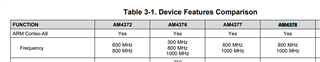

On the datasheet Table 3-1, AM4378 ARM Cortex-A9 is specified as 800MHz/1000MHz.

Does that mean other frequency, for example 600MHz or 300MHz, is not supported?

Is it possible to operate AM4378 with 600MHz or 300MHz? If yes. Could you share how?

Best regards,

Kurumi