Hello,

I am trying to send 16bit words via tsip, using EVMK2EX evaluation board and "TSIP_K2E_C66TestProject" (integrated in "pdk_k2e_4_0_16").

The configuration i want to achieve is 32mbit Data rate, 1tx - 1rx lane 512 "physical" timeslots.

I started using TSIP_K2E_C66TestProject as i already mentioned, and i made some changes in tsip.c, tsip.h and tsip_cfg.h files.

Those changes are presented in detail in the attached tsipExample.txt file.

I am facing the following issues.

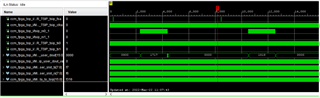

1) Data is not separated in 16bit words in ascending order (as it should be regarding the code in the project), but in big chunks as it is shown in tsip_data_example_1 picture.

2) I constantly get failure messages in both TSIP TEST MODES whenever i change .tsipData and .appData SECTIONS to M2MCSRAM or DDR3 respectively,

this seems to be a DMA issue but I am not sure if it is relevant to my first question or not, how should i manage it?

Thank you in advance!

//------------------------------------------------------------

// tsip.c

//------------------------------------------------------------

...

#define BUFSIZE_TSIP_INST_SHARED 40

/* Buffer size is function of TSIP_N_PORTS */

#define BUFSIZE_TSIP_HEAP_SHARED 200

/* Buffer size is a function of the number of time slots */

#define BUFSIZE_TSIP_HEAP_TIMESLOT 14336

/* Buffer size is a function of the number of time slots and TSIP_N_PORTS*/

#define BUFSIZE_TSIP_TX_DMA_BUFFER 5120

/* Buffer size is a function of the number of time slots and TSIP_N_PORTS*/

#define BUFSIZE_TSIP_RX_DMA_BUFFER 5120

/* Buffer size is based only on the size of the instance*/

#define BUFSIZE_TSIP_INST_SIZE_PORT 176

...

void tsipConfig (tsipSizeInfo_t *sizeCfg, tsipConfig_t *cfg)

{

/* Provide size information for TSIP */

sizeCfg->maxChannels = TSIP_MAX_TIMESLOTS;

sizeCfg->subFrameSize = 8;

sizeCfg->wordSize = 8;

sizeCfg->numPorts = NUM_USED_TSIP_PORTS;

/* Global configuration */

cfg->testMode = FALSE;

cfg->testModeSelect = CSL_TSIP_TESTMODE_LINK_LOOPBACK;

cfg->clkRedund = 0;

cfg->endian = CSL_TSIP_ENDIAN_LITTLE;

cfg->priority = CSL_TSIP_PRI_0;

cfg->maxPriority = CSL_TSIP_PRI_0;

cfg->sizeCfg = sizeCfg;

cfg->maxPhase = 0;

cfg->subFrameCallout = NULL;

cfg->cxt = NULL;

/* Transmit configuration */

cfg->tx.channel = deviceWhoAmI();

cfg->tx.frameSize = CSL_TSIP_FRAMESIZE_128;

cfg->tx.tsPerFrame = 512;

cfg->tx.clkSrc = CSL_TSIP_CLKSRC_A;

cfg->tx.dataDelay = 1024;

cfg->tx.bdxDelay = CSL_TSIP_DLY_CTRL_DISABLE;

cfg->tx.idleDrive = CSL_TSIP_XMTDIS_HIGHIMP;

cfg->tx.fsyncPol = CSL_TSIP_FSYNCP_ALOW;

cfg->tx.fsyncClkPol = 1;

cfg->tx.clkPol = CSL_TSIP_CLKP_FALLING;

cfg->tx.dataRate = CSL_TSIP_DATARATE_32M;

cfg->tx.clkMode = 1;

cfg->tx.superFrameInt = CSL_TSIP_INT_ACK;

cfg->tx.frameInt = CSL_TSIP_INT_ACK;

cfg->tx.frameIntDelay = 0;

/* Receive configuration */

cfg->rx.channel = deviceWhoAmI();

cfg->rx.frameSize = CSL_TSIP_FRAMESIZE_128;

cfg->rx.tsPerFrame = 512;

cfg->rx.clkSrc = CSL_TSIP_CLKSRC_A;

cfg->rx.dataDelay = 0;

cfg->rx.bdxDelay = CSL_TSIP_DLY_CTRL_DISABLE;

cfg->rx.fsyncPol = 1;

cfg->rx.fsyncClkPol = 1;

cfg->rx.clkPol = 1;

cfg->rx.dataRate = CSL_TSIP_DATARATE_32M;

cfg->rx.clkMode = 1;

cfg->rx.superFrameInt = CSL_TSIP_INT_ACK;

cfg->rx.frameInt = CSL_TSIP_INT_ACK;

cfg->rx.frameIntDelay = 0;

}

...

/* Companding and phase */

ctl->compand = CSL_TSIP_TIMESLOT_LINEAR;

ctl->phase = 0;

/* Transmit direction */

ctl->tx.enable = TRUE;

ctl->tx.timeslot = timeSlotLinkPort;

ctl->tx.frameSize = 16;

ctl->tx.callout = appToTsip;

if(tsipPort==0)

{

ctl->tx.context = (void *) &toTsip0[timeSlot];

ctl->tx.buffer = (tsipData_t *) &appToTsipBuffer0[timeSlot * BUFSIZE_APP];

}

else

{

ctl->tx.context = (void *) &toTsip1[timeSlot];

ctl->tx.buffer = (tsipData_t *) &appToTsipBuffer1[timeSlot * BUFSIZE_APP];

}

/* Receive direction */

ctl->rx.enable = TRUE;

ctl->rx.timeslot = timeSlotLinkPort;

ctl->rx.frameSize = 16;

ctl->rx.callout = tsipToApp;

//------------------------------------------------------------

//------------------------------------------------------------

// tsip.h

//------------------------------------------------------------

...

/* Number of TSIP ports used in the test */

#define NUM_USED_TSIP_PORTS 1

/* This test uses the same number of time slots per TSIP port being tested*/

/* Number of used time slots per TSIP port (same for all ports)*/

#define NUM_USED_TIME_SLOTS 256

...

//------------------------------------------------------------

//------------------------------------------------------------

// tsip_cfg.h

//------------------------------------------------------------

/**

* @def TSIP_MAX_TIMESLOTS

* The maximal number of TSIP timeslots to be used

*

*/

#define TSIP_MAX_TIMESLOTS 256

//------------------------------------------------------------

//------------------------------------------------------------

// test.cmd

//------------------------------------------------------------

SECTIONS

{

.tsipData > L2SRAM

.appData > L2SRAM

}

//------------------------------------------------------------

//------------------------------------------------------------

// test.cmd 2nd question

//------------------------------------------------------------

SECTIONS

{

.tsipData > MSMCSRAM

.appData > MSMCSRAM

}

OR

SECTIONS

{

.tsipData > DDR3

.appData > DDR3

}

//------------------------------------------------------------