Hi Support Team,

I have questions about the MIN values for Input signal rise time and Input signal fall time.

Q1: Regarding Input signal rise time and Input signal fall time in the datasheet "5.12.17.1 MMC Electrical Data and Timing",

is it necessary to strictly observe the MIN value of 1ns?

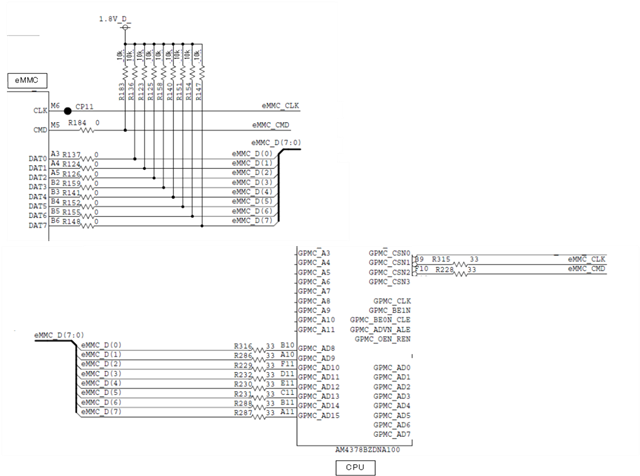

The current schematic is as follows.

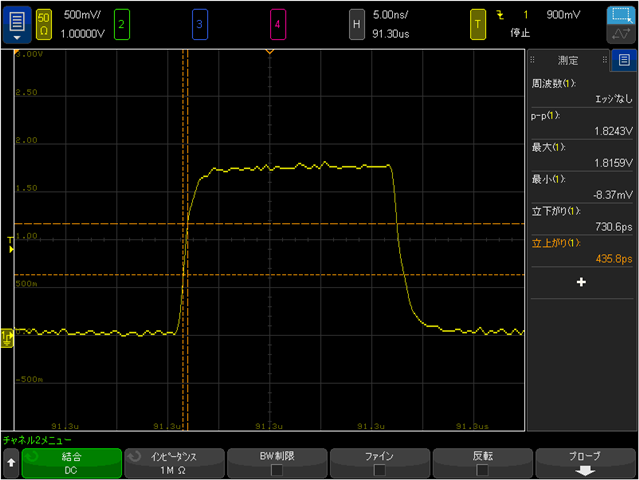

The waveform of DAT3 from eMMC to CPU is shown below.

The time axis scale has not been expanded in relation to the transition time, but it is within 400 to 500 ps.

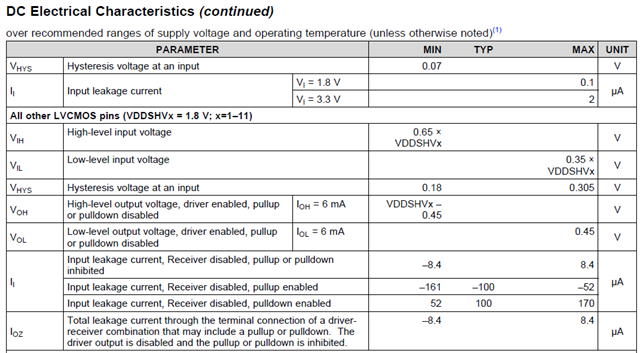

The thresholds for rise time are as follows

VILmax: 0.65*1.8=0.63V

VIHmin: 0.35*1.8=1.17V

*Used with 1.8V VCCQ

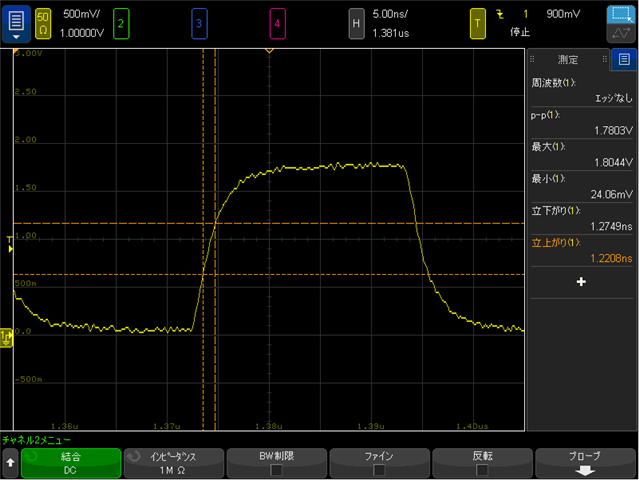

The waveform after the constant change is shown below.

The constants after the change are as follows

Damping resistor on CPU side: 56Ω

Damping resistance on eMMC side: 100Ω

External pull-up resistors on CMD and DATA (7:0) lines (pull-up near eMMC): 10 kΩ

Q2. I checked the following thread. is the rise time specified from 10% to 90% instead of VILmax to VIHmin?

e2e.ti.com/.../am437x-input-signal-rise-time-and-fall-time-from-nand-flash-memory

For eMMC, JEDEC stated VILmax to VIHmin, so we measured the same period.

Best regards,

Kanae